LDICA [Lineage and Digital Portegorated ciacuit

-Applications).

Hodule 1: Integrated cincuits and openational Amplifiers

\* Integrated cigratit [IC]: - Integrated circuit where all compon -ents like active and passive components are fabricated

on a single chip of silicon (si).

\* All the active elements like transister and diode and Passive elemente like Resistor, Inductor, capacitor are tabricated on a single piece of semiconductor material (si).

\* Advantages of 2c Technology:

- · Hiniaturization and (or) small in size and hence increase the equipment density.

- · Low cost due to batch processing.

- · Improved system reliability due to the elimination of soldered joints.

- . Better functional performance.

- · Matched devices.

- . Increased operating speeds.

- · Low supply voltages.

- . Less weight [weight of Re much less compared to descrete ciacuit consisting of same number of components.

\* classifications of 715:

Integrated circuits offer a wide grange as applications and are broadly classified as.

- · Linear Dis

- · Digital Ris

- · Linear Dis: Linear Dis accepts analog input and delivers analog output

- · The gelationship between the input and output of a circuit is linear.

Ex:- operational amplifier Cop-amp].

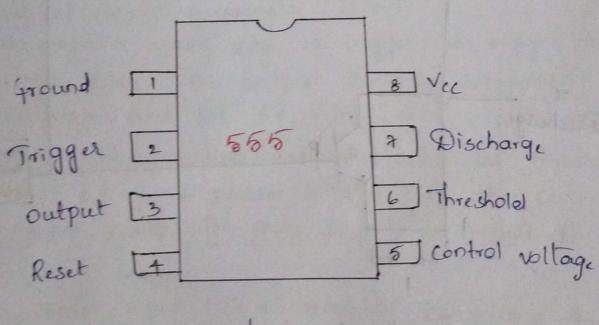

- · Timer 2c 555

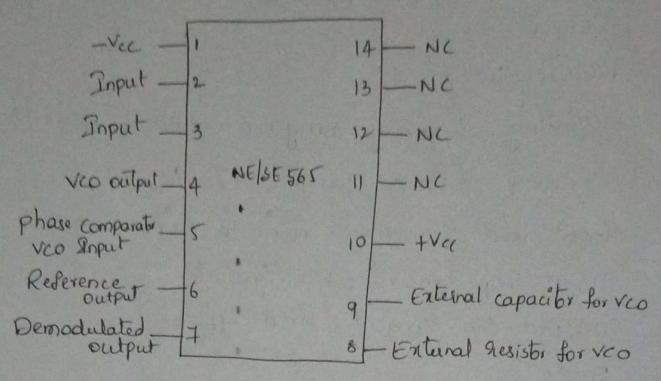

- · Phase locked loop Ic 565.

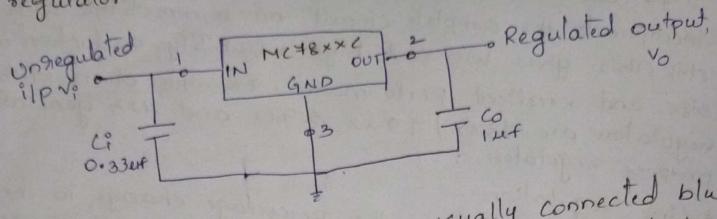

- · Voltage Regulator 2c 423.

- . Waveform generator Pc [8038].

- \* Digital Dis: The circuit is either in off-state and not in between the two.

- · Digital Ic's accepts input in two discrete voltages. levels: logic o (Zero) or logic 1 [+5v]. The output is also discrete in two specific voltage levels only.

i-e Zero (0) & one (1)

. Hence noise immunity is better in digital circuits compared to analog circuits

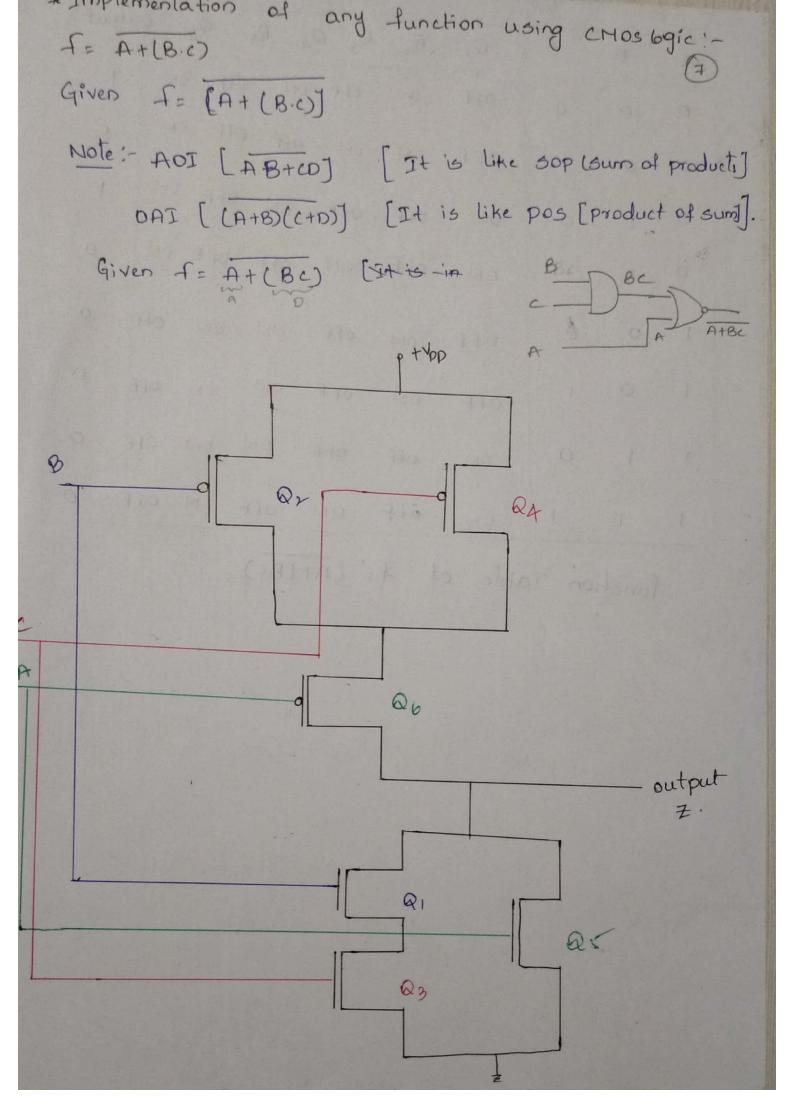

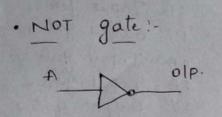

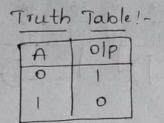

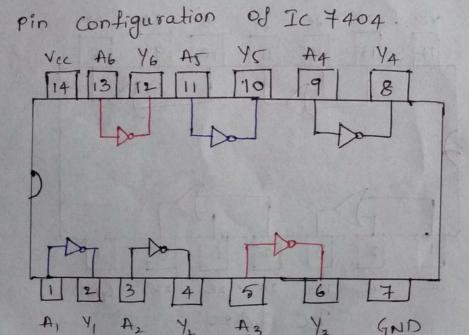

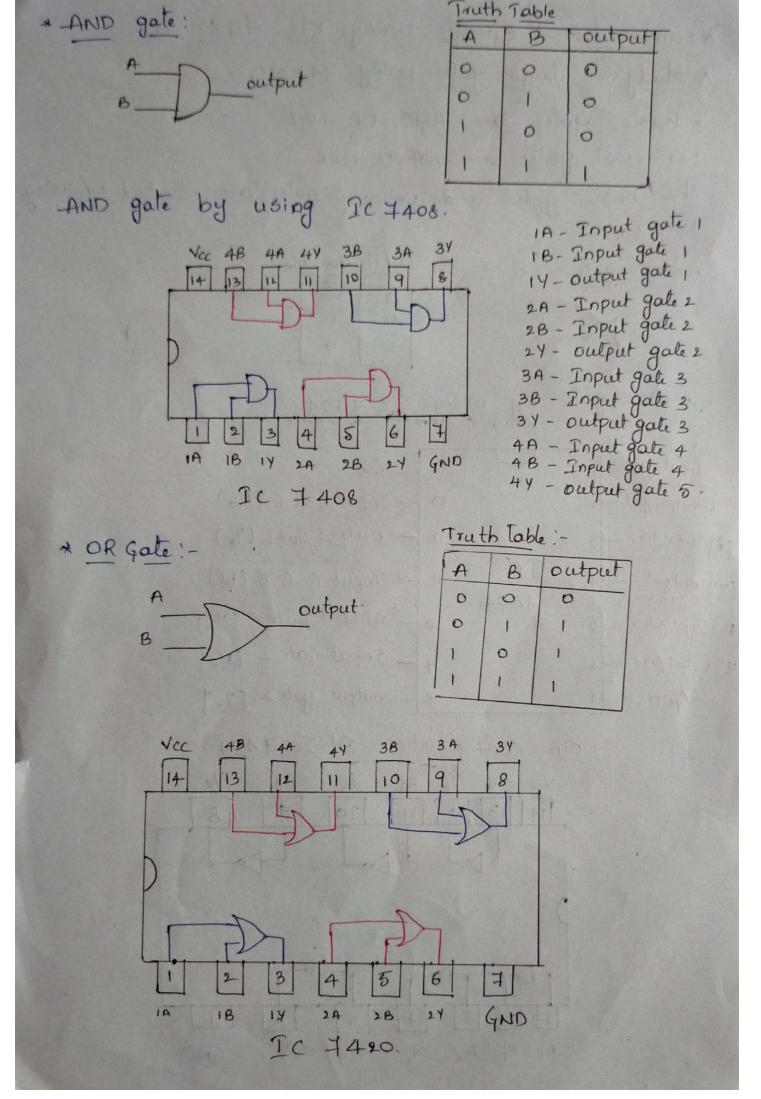

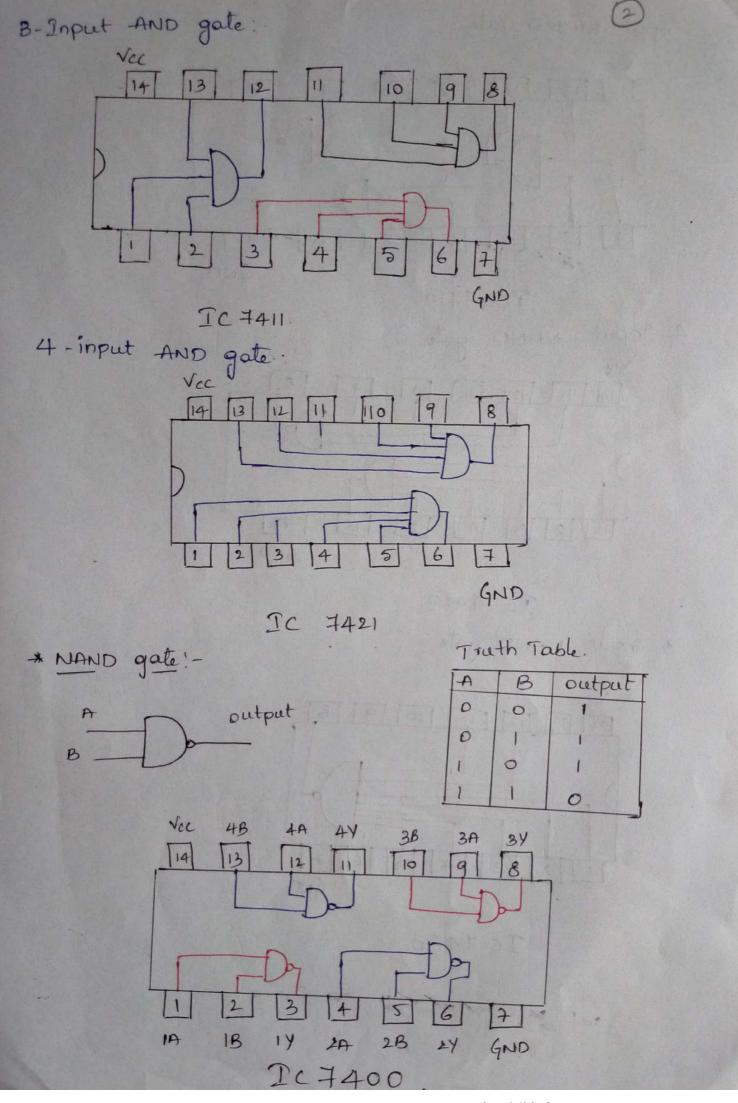

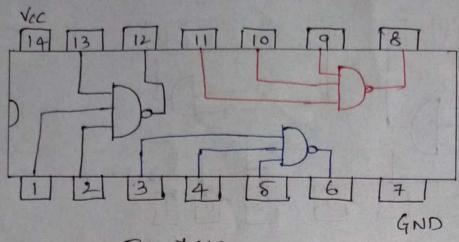

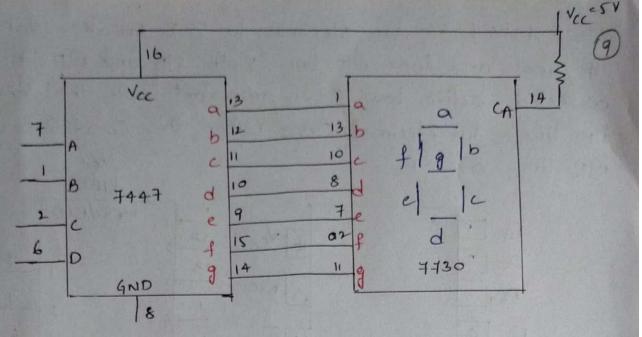

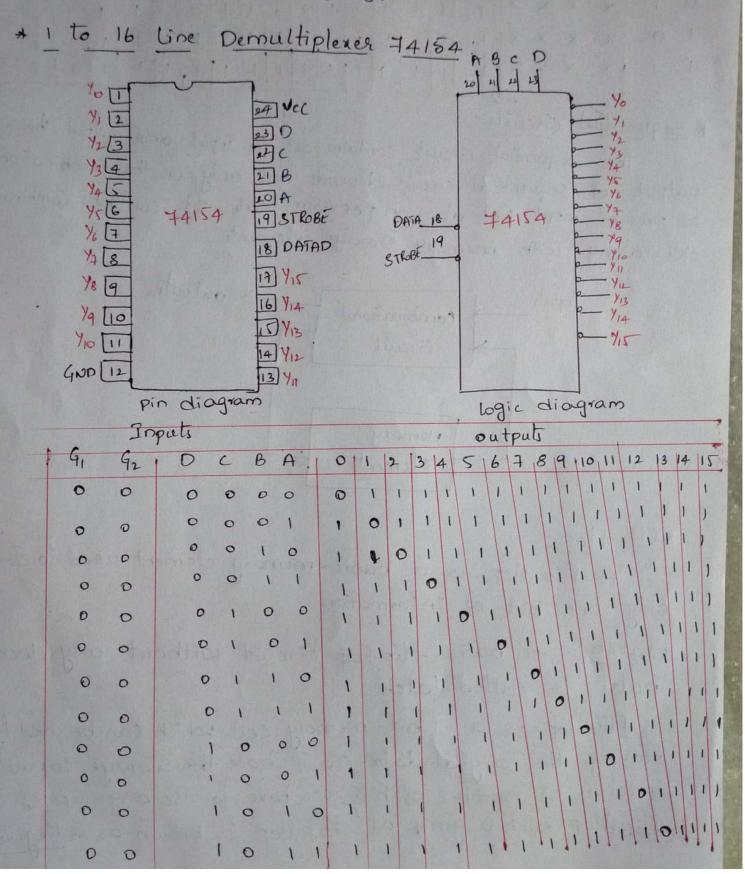

Ez:- Logic gates 7400, 7404 Multiplexers

Hicroprocessor 8085, 8086, 80486.

· Based on technology used. Pes are classified as.

i, Monolithic Ic's

iii thin and thick Irlm De's.

iii, Hybrid Das.

· Monolithic Ris:

The word monolithic comes from the Greek word 'monos' and 'lithos' which means 'single' and 'stone'. . The monolithic De's grefer to a single stone or a single crystal.

· The single crystal refers to a single silicon strickip as the semiconductor material on top of which all the passive and active components are interconnected.

· Monolithic Ics are considered as the best mode of Hanufacturing Ics as:

1. It can be made identical.

2. High neliability.

3. Hanufactured in bulk in very less time

4. low cost.

+ limitations:

· Low power nating.

· cannot be used for high power applications as it can't have power nating of more than Iw.

· The isolation beliveen the components within the integrated circuit is poon.

. The passive components within the Ic will have small value and an external connection is required from the Ic pins to obtain high values.

\* Thin and Thick film Ic :-

· These Des are larger than monolithic Des and Smaller than discrete exti.

. It can be used in high power applications.

· Diodes and transistors if required can be extremally connected on to its corresponding pins.

\* Hybrid Pis :-

· The circuit is fabricated by interconnecting a number of individual chips.

· Used for high power audio amplifier applications.

· In Hybrid Res separate components are attached to ceramic substrate and interconnected by means of either metallisation pattern or wire bonds. This either metallisation pattern or wire bonds. This technology is adaptable to small quantity custom circuits.

· Based on active devices used Monolithic Pc's are further classified as bipolar Pc's and unipolar Tc's.

Antegrated circuits

Honolithic circuits

Hybrid circuits

Bipolar

Unipolar

P.N Junction Dielectric Mosfet Jfet.

Psolation Isolation classification of Icis.

\* Ic size and cincuit complexity: \* The invention of the transister in 1947 by william B. Shockley, watter H. brattain and John Bardeen of Bell laboraties was followed by invention of Ic. \* The concept of Ic was introduced at beginning of 1960 by with Texas Instruments and Sairchild \* The first Integrated circuit has only a few devices, Semiconductors. Perhaps as many as ten diodes, transistors, Resistors and capacitors making it possible to fabricate one or more logic gates on a single chip. \* As an increasing the number of components log transistor Per integrated circuit the technology was developed as · Invention of 1947 Transistor (Ge) 1955-1959 · Development of Silicon transistor Junction transistor diode 1959 · silicon plana91 3 to 30 gates chip approx. or Technology 1960-1965 . first Ics, small 100 transistors Ichip [logic gate, scale Integration [35] flip-flops] 30 to 300 gates chip or 100 1965-1970. · Medium scale to 1000 transistor 1 chip Integration [MS] (Counters, Multiplezers, Adders] 300 to 3000 gates Ichip or · large scale Integra 1970-1980 1000-20,000 transistors | chip -tion [LSI] 18 bit microprocessors, ROH, RAM

1980-1990 More than 3000 gates chip or · very Large Scale Integration 20,000 - 1,00,00,00 transistors / chip (16 and 32 bit micropiol. [VIST] -essors) 1990-2000 106-10 transistors / chip · Ultra large [special processors, Virtual scale Integration reality) machines, smart sensors (01557 · Giant-scale > 10+ transistors | chip. Embedded systems, systems Integration (GSI)

\* Linear integrated cincuits are being used in a number of electronic applications such as fields like audio, Radio

communication, medical electronics, etc. \* An important linear 2c is operational amplifier.

\* operational Amplifier: - [Abbreviated as op-Amp].

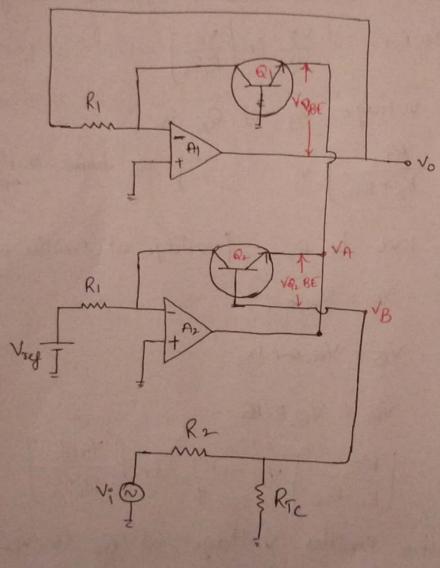

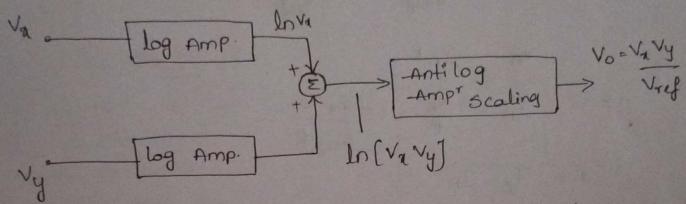

operational Amplifiers used to perform several applications like adder, subtractor, multip differentiator

and integrator.

· op-Amp is a directly coupled high gain Ic amplifies with two high impedance input terminals and one low output impedance. The op-amp consists of a differential amplifies input stage and an Emitter follower output

· An operational amplifier available as a single

integrated circuit package.

. It can be used to amplify dc as well as ac input signals and was originally designed for computing such as operational or mathematical operations like addition, subtraction, Multiplication, differentation and integration.

ewith the addition of suitable external feedback components the op-amp can be used for a variety of applications such as ac and de signal amplifications, active filters, oscillators, comparators, regulators etc.

op-Amp

General purpose op-Amps

They can be used for a variety

of applications such as

They can be used for a variety

of applications such as

Differentiator

Burning Amp and others

Ex: widely used general purpose

op-amp is 741.

Special purpose op-amps.

They are used only for

the specific applications

Ex: LM 380 op-Amp is

used only for audio

power applications.

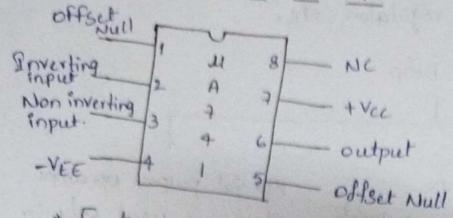

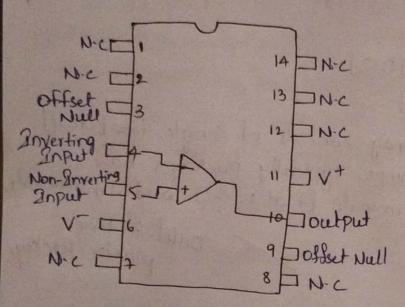

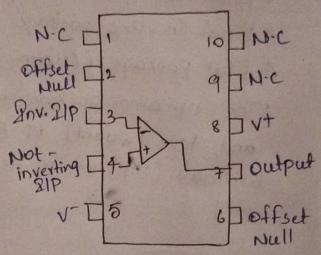

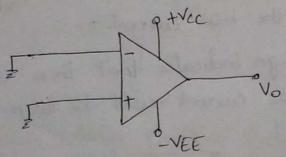

\* Schematic symbol of Ic 141:

2 Investing input.

V1 - 2 - 4 + vo output terminal

Non Inverting

input.

-VEE [-ve supply voltage terminal]

\* The positive input is the non-inverting input. An ac signal [lor) de voltage] applied to this input produces an inphase [or same polarity] signal at the output.

The negative input is the inverting input An ac signal [or de voltage] applied to this input produces out-of-phase [or opposite polarity] signal at the output.

Noltage at the non inverting Input [volt]

Noltage at the Inverting Input [volt]

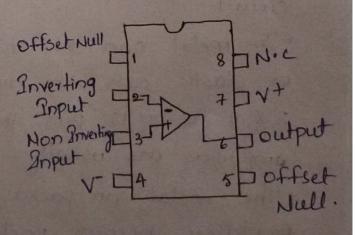

No - output vollage [volls] A - large signal vollage gain \* PIN Diagram of To 741

\* features of 741 op. Amp:

· Short circuit and overload protection provided.

· large common mode rejection ratio [CMHR] and différential vollage ganges.

Ideally CMMR is indinity

. No external frequency compensation is required. It also does not need any external compensation for phase component. This simplifies the circuit design and minimizes the number of components

· off set voltage null capability.

. No latch-up problem

· low power consumption.

\* 2 dentification code :-

1. Fair child - MA, MAF.

2. National semiconductor. LM, U, 3H

3. Motorola - MC

4. NEISE, NIS - signetics

5. Burr - Brown BB

6. Texas Instruments

7. RCA CA, CD

8. Intersil ZCA.

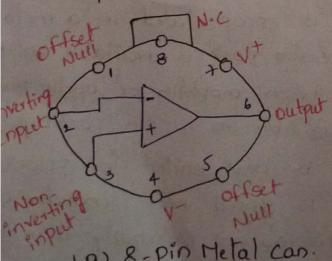

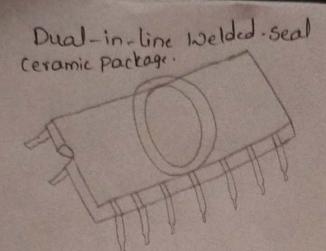

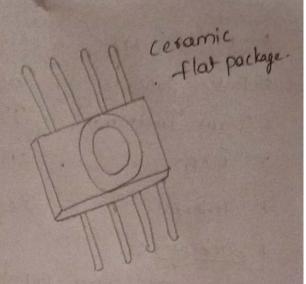

\* Packages :-

. There are three popular packages available.

\* Metal can (To) package.

\* Dual-in-line package [DIP].

\* Flat package, (ceramic)

· The op-amp packages may consists of single, two [dual] and four [Quard] op-Amps. Typically packages have 8 terminals [DIP] (or) 10 terminals [flat packs] and 14 terminals Dull-in line

[DIP]

Top-5-style package Tab locates Pin 8

plastic Package

, b) 8-Pin Hini DIP.

, c, 14-lead dual-in-line Package (d) 10-lead flat Pack.

\* The flat pack comes with 8, 10,14 or 16 leads. These leads accommatate the power supplies, Inputs, outputs and several special connections required to complete the circuit.

In metal can the chip is encapsulated in a metal or plastic case the transistor pack is available with 3,5,8, 10 ion 12 pins the power amplifier or audio power amplifiers are usually available in 5-pin package.

\* The metal can package is best suited for power Amplifiers because metal is Agood heat conductor and consequently has better dissipation capability than the

Ilat pack or Dual-in-line package. Host of general purpose op-amps come in 8, 10 or 12 pin package

\* In the dual in line package [DIP] the chip is mounted inside a plastic or Ceramic Case.

\* The DIP is most widely used package type because it can be mounted easily. The 8-pin DIP packages are referred to as mini DIPS. DIPS are also available with 12, 14, 16 and 20 pins.

\* As the density of components Integrated on the same chip increases the number of pins also goes up.

\* In plat pack the chip is enclosed in a rectangular ceramic case with terminal leads extending through the sides and ends.

\* Temperature Ranges:-

Ic's are manufactured in three standard temperature manges.

c: commerial o'c to 70°c

2: Industrial -25°c to +85°c

M: Military -55°c to +125°c.

\* The very commonly used general purpose op-Amp is 2c 741.

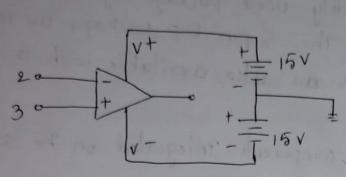

\* power supply connections:

The v+ and v- power supply terminals are connected to two dc vollage sources.

\* The Vt pin connected to positive terminal of one Source of V pin connected to negative terminal of other source where two source are 15V batteries each.

power supply voltage singes from ± 5v to ± 22v. The common terminal of V+ and V- source connected to ground, otherwise twice the supply voltage gets applied and damage the op-Amp.

Ic will not function properly is power supply connections are not given.

\* Advantage of OP-Amp over transistor Amplifier

- · Low Power consumption

- · Low cost

- · More compact [22 is small or tiny]

- . More geliable.

- · Higher gain can be obtained.

- · Easy design [ It to design inverting complifier only two resistors will be connected. J.

- \* op-Amp is a very high gain amplifier fabricated on

- \* Combination of many transistors, fers, resistors in a pin head space.

- \* Applications !-

- · Audio Amplifier.

- · signal Generator.

- · signal fillers

- · Biomedical Instrumentation.

Etc.

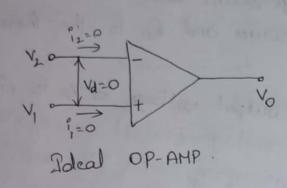

\* Ideal Op-Amp:-

+ The Op-Amp has two input terminals and one output terminal.

\* The '- & + ane the inverting and non inverting input terminals nespectively.

V=0 Vo=V, [an phase]

Equivalent circuit of op-AMP.

\* Characteristics of Ideal op-Amp:

\* open loop vollage gain is infinity AoL=10.

open loop due to no feedback and vollage gain is infinite because  $V_1 = V_2 = 0$ .

· But practically the vollage gain is very high.

[i.e 2, 50,000].

\* Infinite input impedance Ri=00.

· [No current flows into input].

. To avoid loading effect on preceding stages.

· But in practical Ri is 1012 st for fet input op-Amps.

\* Zero output impedance Ro=0.

[ To connect infinite loads]

. Practically current is maximum.

\* The op-amp output will do whatever it can

[within its limitation] to make the voltage difference between the two [ $Vd = V_1 - V_2 = 0$ ]. 3eto.

\* Infinite Bandwidth Bw= or Callows Imin to Imax

\* Indinite common mode Rejection Ratio CHMR=00.

\* Indinite slew gate.

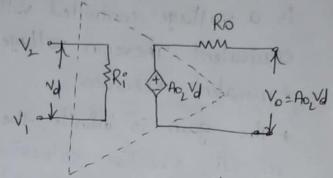

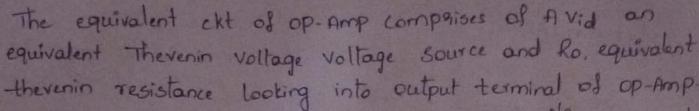

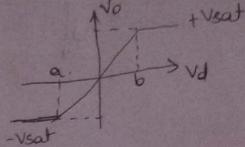

\* A physical amplifier is not an ideal one. The op-Amp is a voltage controlled voltage source and AoLVd is an equivalent Thevenin voltage source and Ro is the Thevenin equivalent Resistance.

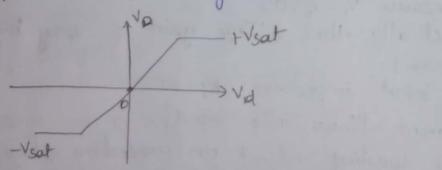

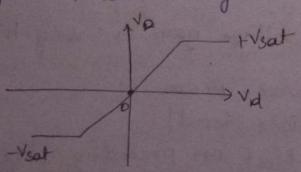

\* The gain is infinite, the output voltage is vo is either at its positive saturation voltage (+vsat) or negative Saturation voltage (-vsat) as v, >v, vesp.

\* One of the two possible output states that is that only.

\* This has a limited applications Such as voltage comparator, Zero crossing detector etc.

· An ideal op-amp draws no current into both the input terminals i.e 1=1,=0. Because of infinite input impedance, any signal source can drive it and there is no loading on the Preceding driver stage.

\* The output vollage is independent of current. drawn from the olp gesistance [Ro=of: Thus op-Amp can drive infinite number of devices.

[within its limitation] to make the voltage difference between the two [ vd = v, -v, = 0]. Beto.

\* Infinite Bandwidth Bw: 00 (allows Imin to Irrax)

\* Infinite common made Rejection ratio CHMR=00

+ Indinite slew gate.

\* A physical amplifier is not an ideal one. The op-Amp is a voltage controlled voltage source and AozVd is an equivalent Thevenin voltage source and Ro is the Thevenin equivalent Resistance.

\* The gain is infinite, the output voltage is vo is either at its positive saturation voltage (+vsat) or negative Saturation voltage (-vsat) as v, zv, or v, zv, resp.

\* one of the two possible output states that is +1/sat on -1/sat and the amplifier acts as a switch only.

this has a limited applications such as voltage comparator, Zero crossing detector etc.

An ideal op-amp draws no current into both the input terminals i.e 1,=1,=0. Because of indinite input impedance, any signal source can drive it and there is no leading on the preceding driver stage

\* The output vollage is independent of current. drawn from the olp gresistance [Ro=of Thus op-Amp Can drive indinite number of devices:

\* Practical op-Amp:

Vo = Avid = A[V1-V2]

A - Open loop vollage gain Vid - disserential ilp vollage

V2 - Voltage at inverting isp terminal

V, - Vollage at non-inverting ilp terminal.

\*The old voltage vo is directly proportional to algebraic difference blue two ild voltages

\* op-Amp amplifies the difference blue two ilp vollages

\* Open Loop Configuration of op-Amp:-

· open loop connection: no direct connection between output and any of the input terminals.

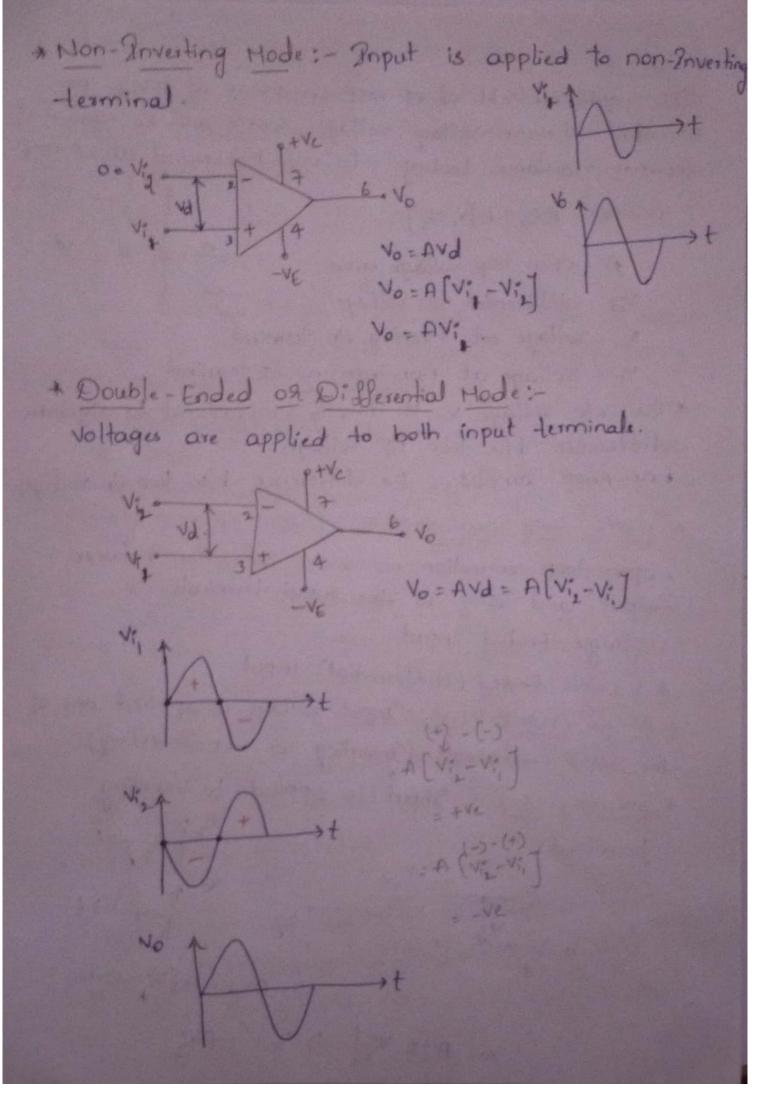

1. Single-Ended input.

2. Double - Ended (differential) input.

\* single-Ended input: - Input voltage is applied one of

the input terminals (Inverting or non-Inverting).

\* Inverting Mode: - Input is applied to inverting terminal.

Vo= A[0-Vi] => Vo= -AVi2

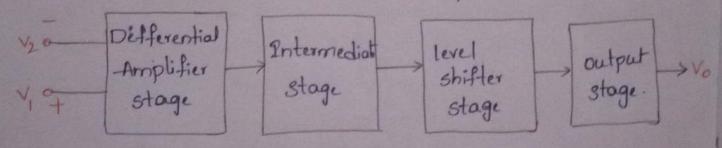

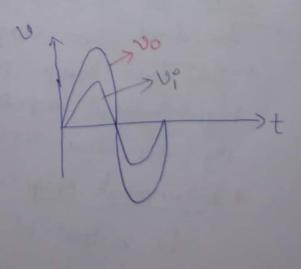

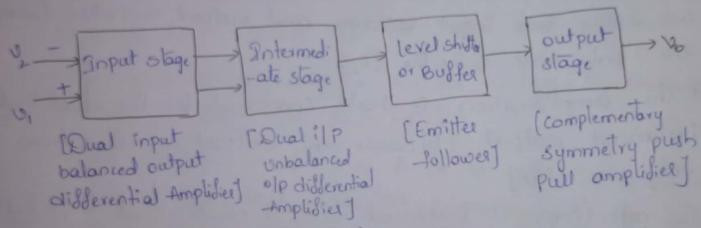

## \* Internal block diagram of op-Amp:

\* Input stage or differential amplifier stage can amplify difference between two input signals, input gresistance is very high. Draws Zero current from the input source.

\* Intermediate stage uses direct coupling; provide Very high gain

\* level shifter stage shifts the de level of output Voltage to Zero [ can be adjusted manually using two additional terminals]

\* output stage is a power amplifier stage; has very small output resistance, so output voltage is same, no matter what is the value of load resistance connected to the output terminal.

fig: Block Schematic of an op-Amp.

\* The essential building block of modern Ic

op-amp is differential amplifier.

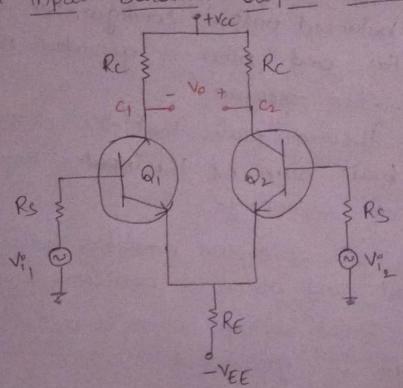

\* Differential - Amplifier: -

. The di.

A ciquit that amplifies the difference between two signals is called a difference or differential amplifier. It is able to suppress any undered noise which is common to both the ilp terminals.

\* A differential amplifier can be used in four different : Configurations depending upon the number of input signels used and the way output is taken.

· The four configurations are.

1. Dual input balanced output (or) Differential Input, differential output.

2. Dual input unbalanced [single ended] output

differential amplifier.

3. Single input balanced output differential Amplifier.

4. Single input unbalanced [single ended] output differential amplifier.

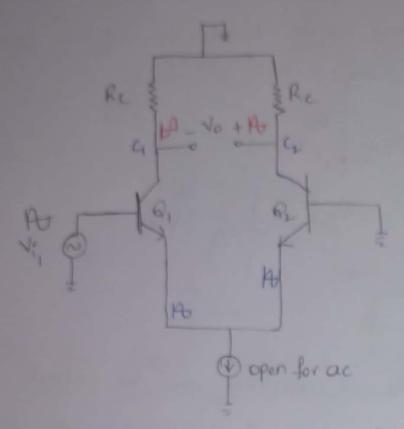

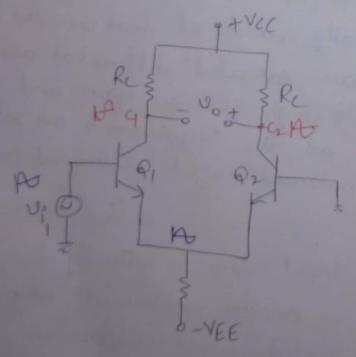

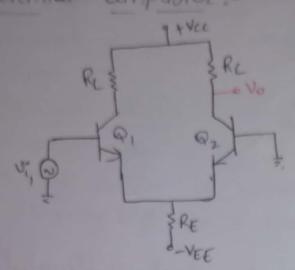

\* Dual input balanced output differential Amplifier:

- the purpose of RE and dc Source - VEE supply constant emitter current.

\* In ac analysis we can replace RE & VEE by a constant current source.

analysis the de vollage source are and de current source are opened. grounded

\* The circuit has two input voltages Vi, & Viz. In dual input balanced output configuration the one input is active and other is grounded. Here we apply Superposition theorem.

- + Superposition theorem states that the output is equal to the algebraic sum of the input voltage produced by each source separately.

- \* VI, and VI, are differential amplifier voltages one is inverting input and other is non-Inverting input.

- \* one of the input vollage source is active and other input voltage is grounded.

- \* The output is taken at the collector of the transistors Q, and Q2.

\* Here Q, forms a CE amplifier CE Amplifier shows the output invester of the input so amplified output will be at the G.

\* At the Emitter the output is no phase inversion.

\* The input for 0, is applied at the Emitter and base is grounded of forms CB amplifier.

\* Because of vi, the net output vollage is:

vo, is obtained by adding olps of GE - olp of & G-roninverted of A. Added write C.

\* O, transistor provides non investing input

Vo, = A.Vi, [where A - Voltage gain]

\* Now, consider the input vollage Viz is active and UP, is grounded

the Q, forms the CE amplifies and the output is inverted at C2.

\* 6, forms the cB amplifier and the output is without any inversion.

To to the state of the state of

Input

output

\* 0, transister [vi,] provides Inverted input.

Voz = A Viz

· Apply superposition theorem

Vo = Vo, + Vo2

Bince Vo, & Vo, disfers in phase by T.

Vo = AVi, - AVi2

No = A[Vi, - Vi2]

Vo = A Vd [: Pd = Vi, -Vi2]

Vid = disserence voltage

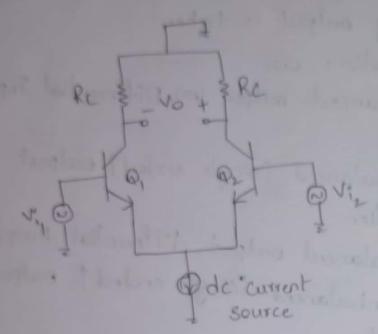

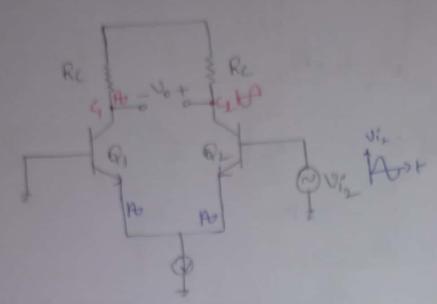

\* Dual input unbalanced [single ended] output Districtial

Amplisher: (1)

Re Re Vo

R

we apply two input voltages and output is taken from the only one collector [C,].

\* The amplification is half compared to the dual input balanced output [because the output is taken from only one side].

\* Single input balanced output differential Amplifier:

Vo = AV;

\* single input unbalanced [single ended] output

differential amplifies:

to the single input balanced output.

\* No advantage over Simple CE amplifies. Almost never used.

-fig: Schematic of op-Amp

\*The Ic op-amp usually consists of four cascaded block.

The first two stages are cascaded differential amplifies.

\* The first stage provides high voltage gain and Very high himput impedance all the requirements are satisfy by the dual input balanced output Differential amplifies.

\* Intermediate stage:-

The output of the input stage is directly fed to the Intermediate stage This is another differential amplifies with dual input unbalanced output differential amplifies.

The main function of the intermediate stage is to provide an additional voltage gain required practically the intermediate stage is a chain of cascaded amplifier called multistage

\* Budder / level shifter :-

Zero De

level.

additional

The third stage is acts as a budder as well as a level Shister The busser is usually an emitter follower. whose input is very high so it prevents the loading of high gain

\* Due to unbalanced output they is a dc component in output so it shifts the de levels and adds power

\* The level shifter adjusts the dc voltages so that output voltage is Belo Sor Bero inputs

\* The increase in dc level tends to shift the operating point of the next stage . This inturn limits the output voltage swing and may even distort the output signal

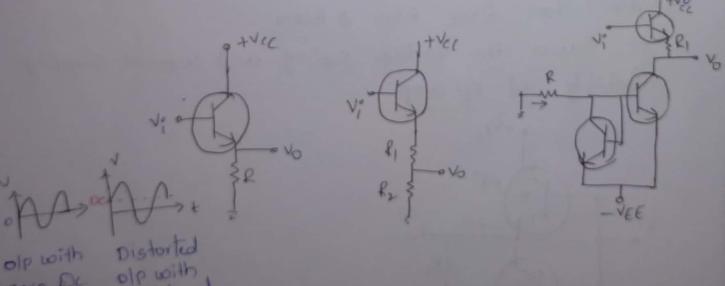

- Fig: level shifter using Emitter follower

\* output stage :-

The function of the output voltage stage in an op-amp is to supply the load current and provide a low impedance output. It should also provide a large output voltage in Ver + VEE

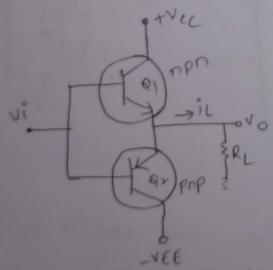

+ A simple output stage consists of two complimentary transistors Q, [npn] and Q, [pnp] connected as a Emitter follower.

to load R. to load R.

acts as a sink to remove current from the load R.

the limitation occurs lies output voltage vo remains zero until the ilp vi exceeds vBE (cut in) = 0.5 v. This is called cross over distortion the cross over distortion on be eliminated by applying a bias voltage slightly greater than 2 vBE blue 2 Bases.

\* It haises the voltage swing and current supply capability of op amp.

Complementary Emitter follower ofp stage

## \* De characteristics :-

\*An ideal op-amp draws no current from the source and its response is also independent of temperature However, a real op-amp does not work this way.

\* Current is taken from the source into the op-amp inputs.

\* Input offset voltage (No):-

If the input voltage V, & V, [Inverting and non-inverting] input is given as selo then the output should be selo

\* Assume V, =0 & V,=0 and if the opamp is ideal then the output should be 3elo. But due to the biasing voltage the output is offset [small amount of output] This is called as Input offset voltage.

\* To nullify the offset voltage that means to make the output voltage as selo. Apply the required voltage at the input terminal of op-Amp.

Vio = ov [Ideal]

Vio = 100er [Practical]

\* Input offset current:

\* For ideal op-Amp input impedance Ri = 10 but practically it is not true. The Op-Amp draws current from input de Voltage Source.

\* The different between the currents entering into the inverting and non-inverting terminals is geterated as input offset

current

12:01 = 128 - IB 1

To +VCC ovo

Here 28 & 28 are the bias currents.

\* The absolute value sign indicates that there is no way to Predict which of bias current will be larger.

2:0 = OA [Ideal]

210 = 100mmnA (practical)

\* Input Bias current (2B):-

consider the base currents entering into inverting and ron-inverting terminals as 28 & 28 grespectively. Even though transistors are identical, but 28 & 28 are not exactly equal due to internal imbalance blue the two inputs.

\*The input bias current is the average value of base current entering into the investing and non-inverting terminal of the op-amp.

28 = 0A [8deal]

2 B = 5000A [Practical]

\*Input Resistance (Ri):-\* This is the differential input gesistance of Ic observed at the either the inverting or non-inverting input terminal, with the other terminal connected to ground. Ri=Os [Ideal] Ri = 1012 so for FET Ri = 2KS2 [Practical] for Pc741 \* Input capacitance (Ci):-\* this is the equivalent capacitance of Se measured at either inverting or non-inverting terminal with the other terminal connect to ground. Ci = Opt [Ideal] Ci = 1.5pf [ practical] \* Input offset vollage Drift: - Vio (drift) It is defined as rate of input offset vollage Vio with temperature (1).

Vio (drist) = 0 [ideal]

Vio (drist) = 0.2 ev/c [practical]

Vio (drist) = dvio uv/c.

\*Input offset current Drift: Dio (Drift)

It is defined as gate of input offset current 2:0 with temperature (7)

Pio (drist) = dio male

Dio (drift) = 0 [Adeal]

=0.1 natoc [practical]

\* Supply current! Is

This current drawn by op-amp-from power supply

Is = 2.8 mA [for 741]

+ Common Mode Rejection Ratio: - [CMRR]:

The relative sensitivity of an op-amp to difference signal as compared to common mode signal is called common Hode Rejection Ratio [CHRR] and gives the figure of merit—for differential amplifies.

1 It is desired as gratio of differential vollage gain (Ad) to common mode voltage gain (Acm)

CMRR = | Ad | Acm |

\* This parameter indicates capability of op-Amp to reject

\* The higher the value of CMRR, the better noise immunity CMRR expressed in decible (dB)

CMRR = 10 Cideal]

CMRR = 10dB [Practical]

\* Power supply rejection Ratio [PSRR]:-

The change in an op-Amp input oddset vollage (Vio) due to variation in power supply vollage + Vic or-VEF is called power supply Rejection Ratio. This is also called as power supply sensitivity

PSRR = Doio uv/v

PSRR = 0 [Adeal] = 150 eV/v [Practical] \* offset voltage Adjustment:

+ for an op-AMP [Je 741] pin number 1 and 15 are provided for making the affect adjustment

the token potentiameter is connected or wiper of pot is connected to -ve supply the wiper of pot is ordinated till vo becomes zero

Range ± 15mV

THE VO

\* Output voltage swing:

This parameter indicates value of the and we saturation voltages of an op-Amp and never exceeds the supply voltage vt and v. The output voltage swing is guaranted blue +13v and -13v for R1 > 212

This gives amount of quiscent power that must be consumed by op-Amp so as to operate properly.

P-85mw.

\* Output Resistance: Ro

output Presistance Ro is gresistance measured blue output

learning of op-amp and ground.

R= on [ideal]

R= 4552 [pratical]

+ output short circuit current: Ise

This is current that may flow if an op-amp gets shorted accidentally and is generally high the op-amp must be provided with short cht protection

Ise : 25mA [for 741]

the Dc characteristics such as bias current, input offset current, offset voltage and thermal drift there will effect the steady state (Dc) gresponse as the op-amp only for small signal sinusoidal (Ac) application. The ac characteristics are frequency gresponse, stability of op-Amp and slewgate.

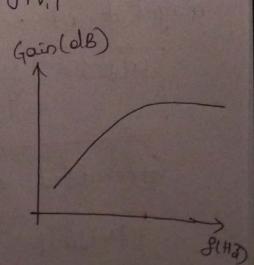

\* frequency gresponse:-

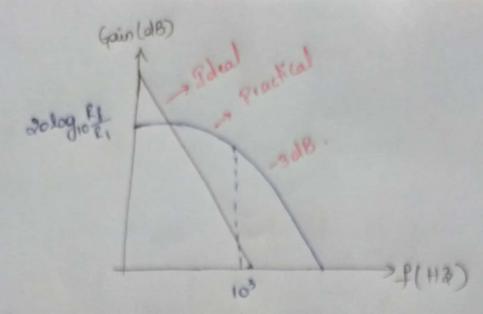

Ideally an op. amp has infinite bandwidth. The open loop gain should gremain constant throughout audio (low) & gadio [high] frequencies.

\*But in practical opamp the gain decreases with increase in frequency (or) gain decreases (9,011 off) at higher frequencies.

\* The gain of opamp goll off after certain frequency due to apacitive component present in equivalent cht of opamp.

\* the op Amp contains the active elements like BJT & The transistors contains junction capacitor all the capacitor are placed by a single capacitor.

\* the capacitance is due to physical characteristics of the device. The high frequency model of an oppmp with signal corner frequency is modified version of low frequency model with capacitor 'c' at olp.

\*There is one pole due to Roc and one -2008/dec 9011-off into effect.

fig: High frequency model of op-Amp with single corner frequency.

\* Open loop gain of op-Amp with one corner frequency is

Where I, is corner frequency (or) 3-dB frequency of op-Amp (or) break frequency. It is operating frequency. + The magnitude and the phase angle of the open loop voltage gain are the function of frequency can be written as  $|A| = \frac{Aol}{1+(B/B_1)^2}$ ;  $\phi = -\tan^4 \left[\frac{4}{B_1}\right]$

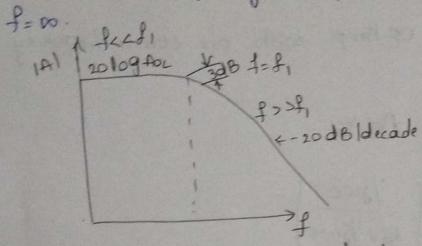

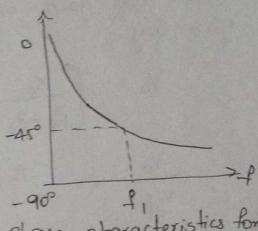

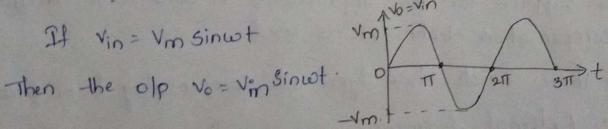

\* Magnitude and phase characteristics:-

i for freq 1224, magnitude of gain is 20logADL in dB ii, For I=1, gain is 3dB drown from for in dB. This -freq fi is called corner freq.

in for foof, gain roll off at rate of - godB/decolon

-6dB/ octave \* from phase characteristics, phase angle is zero at f=0 At corner frequency f=f, \$=-45°, \$=-90° lagging at

open loop Magnitude characteristics phase characteristics for frequercy.

\* The maximum of 90° phase charge can occur in op-Amp with single capacitor.

\* Transfer function in 5-domain given by [with single break frequency)

$$= \frac{A_{0L}\omega_{1}}{\omega_{1}+j\omega_{1}} \Rightarrow \frac{A_{0L}\omega_{1}}{3+\omega_{1}} \left(S=j\omega\right)$$

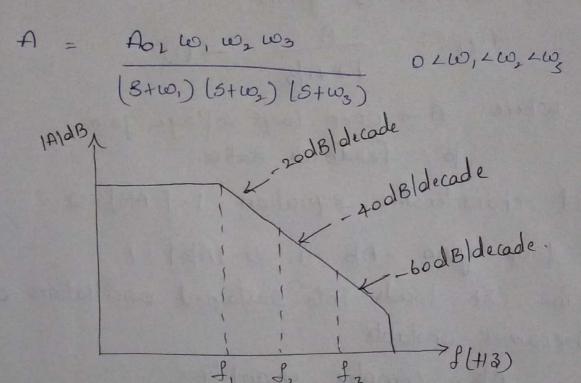

\* A practical opamp has number of stages. Each stage produces capacitive component this is due to number of Rc pole pair. there exist number of break frequency \*Transfer function of an op-Amp (with three break frequencies)

$$A = \frac{AoL}{(1+i8/4,)(1+i(4/42)[1+i4/83]}$$

025,262263

In 8-domain

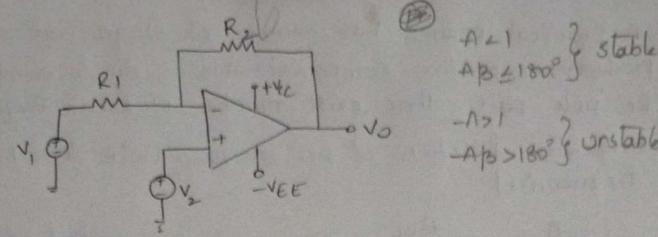

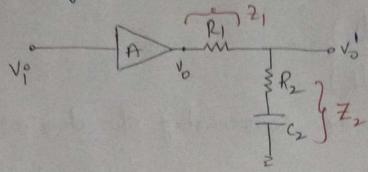

\* stability of op-Amp:op-Amps are rarely used in open-loop configuration due to its high gain.

\* Consider an op-amp It uses Resistor feedback network and may be used as inverting amplified with  $V_2=0$  and as non-inverting Amplified with  $V_1=0$ .

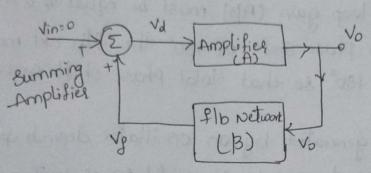

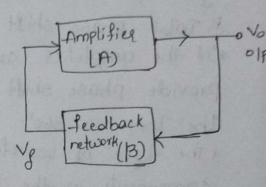

Resistive feedback provided in op-amp I from the negative feedback the closed loop transfer function is given

Ac1 = A - 1 - 1

where A > open loop vollage gain

B - feedback gatio.

\* If characteristics equation 1-[-A/3]=0

loop gain -AB = 1 => 1A|31=1

\* the ckt loads into sustained oscillations and becames unslable

AB- complex quantity.

[AB] = 1 -> Magnitude condition

L-AB=0 or L-AB=TT.

\* In op-Amp, feedback network is resistive now and does not provide the any phase shift since op-Amp used in Inverting mode, it provides a phase shift of 180° at low frequency.

\* At high frequencies due to each number of frequen additional phase shift of max -90° victors with loop gain A

Thus for two corner freq a max of phase shift associated with gain of is -180°

\* Thus at high frequencies, for small values of to the magnitude of Ab becomes unity when A has additional phase shift of 180" which makes total Phase shift equal to Bero.

\* Hence the amplifier begins to oscillater as both magnitude and phase conditions are satisfied thus ascillation is fast starting point of instability

Instability means unbounded olp

(A [1+AB) 41 AB 20 [negative]

\* Aci < A closed loop gain Uses and system is Slable.

for ALL >A closed loop gain +ses and system is unstable.

\* At high frequencies, system A' bee having 3 corner frequencies (on 3 RC pole pair there is charre of open loop gain A to contribute man of -1 to place Shift

\* AB becomes -ve and instability occurs at high frequencies.

\* unstable systems are impractical and need to be made Stable The modification given for stability is used when the system is to be tested practically.

However theoritically analytical or graphical methods are almost used to test system for stability before they are build

-Analytical method - Routh Hurzwith criticaia Graphical method - Bode plot

\* slew rate: -

The slew rate is desine as maximum rate of charge of output voltage with respect to time caused by step input vollage and usually specified in V/us

simple def.: How fast the op-amp dt /max will able to nespord

En: IV/us -> slew rate means that olp raises or falls by IV in lusec.

\* An ideal slew gate is infinite which means op-Amp of voltage should change instantaneously in nesponse to ilp Step vollage

\* op-amp slew rate is related to its freq. Response : Op-Amp with wide bandwidth will have higher slew gate.

\* Practical op-Amp slew rate ranges from 0.11/us to 1000/4 \* The Blew rate improves with higher closed loop gain and De supply vollage. It is also a function of

temperature and generally decreases with an increases in temperature

\* Course of Blew nate:

\* The cause of slew rate is capacitor within (or) outside of op-Amp to prevent ascillation.

\*This internal capacitor which prevents the old vollage from Responding immediately to fast charging ilp.

+ The vollage across the capacitor is given as Ve= - Sidt

\* Here Imax current drawn by op-Amp to Capacitor c.

\* For Faster slew rate op-Amp should have higher current (00) small compensating capacitor.

\* for 741 the max internal capacitor charging current is Limited to about 154A. 30 the slew gate (SR) of 741 is

\* The SR limits the nesponse speed of all large signal wave shapes for sine wave "ilp the effect of slew gate can be calculated

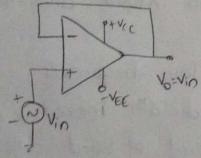

\* let us consider a vollage follower

\* let us consider a vollage follower

\* Assume the ilp signal with high

Voltage (Amplitude) & high freq. Sine wave.

If Vin = Vm Sinut vm 1-5

The state of change of the olp is given by

dt = Vmw caswt.

and the maximum rate of change of the olp occurs when forilp freq. cosut=1 i-e

Vm = Peak value of the sine wave.

SR = 2719 Vm V/115

without the man freq Iman at which is can obtain an undistorted of pollage of peak value vin is given by

Aman = Slew gate

Imax (43) = slew rate 6.28 × Vm

From is also called the full power response it is the max freq of a large amplitude sine wave with which of ump can have without distortion. It either frequency can the amplitude of the ilp signal is increased to exceed the slew gate of the op-Amp the olp will be distorted.

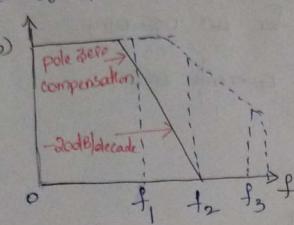

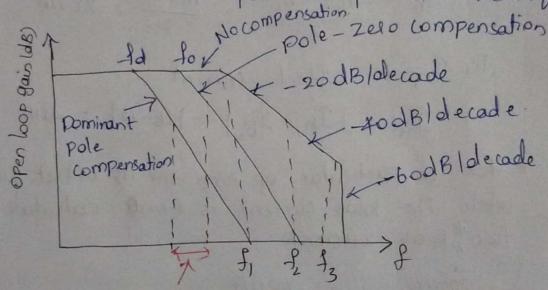

\* Frequency Compensation :-

\* Ideal op. Amp has bandwidth infinite and the open loop voltage is infinite.

\* The gain is constant at low frequencies

\* At high frequency the bandwidth increases noise components To suppress for the improvement of Bandwidth frequency compensation technique is used

\* There existe two types of compensating techniques.

is External frequency compensation

cas Dominant Pole

cb, Pole Zero compensation

ii, Internal compensation.

ri, External Frequency compensation: -

Some types of op-Amps are made to be used with externally connected compensating components specially if they are to be used for Aelatively low closed loop gain.

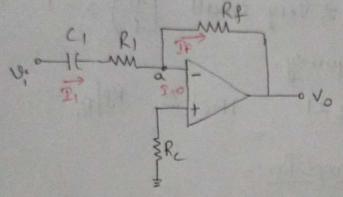

\* Dominant pole Compensation: -

Suppose A is the transfer function or Gain of uncompensated network.

\* A' is the transfer function or Gain of compensated network.

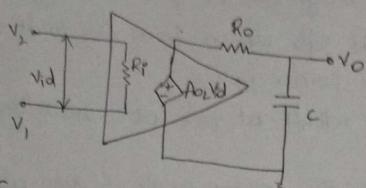

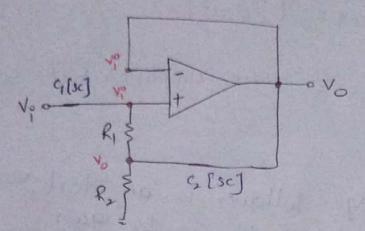

\* Introduce dominant pole by vo A MA' ovo adding Rc nlw in Series with op-amp (or) by connecting capacitor

ic from suitable high resistance point to ground.

$$A' = \frac{V_0}{V_i^{\circ}}$$

$$= \frac{A \left[-\frac{3}{2}\omega c\right]}{R - \frac{3}{2}\omega / c} = \frac{A \cdot \frac{1}{3}\omega c}{1 + \frac{3}{2}\omega c R}$$

The olp voltage  $V_0$

$$\frac{V_0}{R + x_c} = \frac{1}{1 + \frac{3}{2}\omega c R}$$

$$\frac{V_0}{V_i^{\circ}} = \frac{\frac{1}{3}\omega c}{R + \frac{1}{3}\omega c}$$

$$\frac{V_0}{V_i^{\circ}} = \frac{\frac{1}{3}\omega c}{R + \frac{1}{3}\omega c}$$

Vo Vi = 1/jwc R+/jwc

A' = A Wher fa = 1 1+j2TIfCR Wher fa = 2TTRC

$$\int A' = \frac{A}{(1+i\delta/\beta_a)}$$

+ compensated transfer function A' with three corner frequencies

## [1+if/gd) (1+if/g,) (1+if/g,) (1+if/gs)

where fact, < fo < fo

\*The frequency found graphically by having A' pass through odB at the pole f, with slope of -20dBldecade.

\* The value of capacitor can be calculated using

Pd = 1

Disadvantage: -

This compensating technique neduces open loop bandwidth drastically.

Advantage:

The noise immunity of system is improved since the noise frequency components outside the bandwidth are eliminated

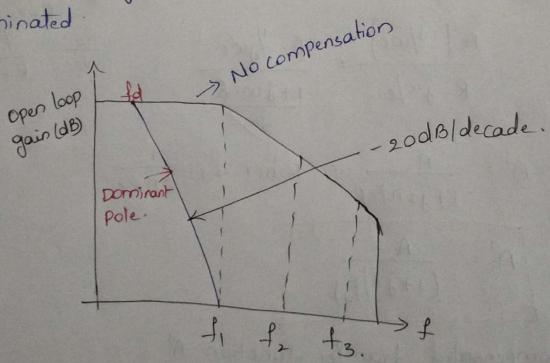

\* pole Zero compensation: -

Here the uncompensated transfer function A' is altered by adding both pole and zero.

\*The compensating now is designed to produce Zero at first corner freq. f, of uncompensated transfer function A this zero will cancel the effect of pole at f.

\*The pole of compensating network to is selected such that compensated transfer function A' passes through odb at second corner frequency for of uncompensated transfer function A

$$\frac{V_{o}'}{V_{o}} = \frac{Z_{2}}{Z_{1} + Z_{2}}$$

$$\frac{Z_{2} - R_{2} + \frac{1}{j\omega C_{2}}}{Z_{2} - R_{2} + \frac{1}{j\omega C_{2}}}$$

$$\frac{R_{2} + \frac{1}{j\omega C_{2}}}{R_{1} + R_{2} + \frac{1}{j\omega C_{2}}}$$

$$\frac{V_{o}'}{V_{o}} = \frac{1 + j\omega C_{2}R_{2}}{j\omega C_{2}R_{1} + j\omega C_{2}R_{2} + 1}$$

$$\frac{V_{o}'}{V_{o}} = \frac{1 + j\omega C_{2}R_{2}}{1 + j\omega C_{2}R_{2} + 1}$$

$$\frac{V_{o}'}{V_{o}} = \frac{1 + j\omega C_{2}R_{2}}{1 + j\omega C_{2}R_{2} + 1}$$

3217 SR, G + 3217 R2 C2+1

$$\frac{v_0'}{v_0} = \frac{1 + i 2 \pi \beta R_2 C_2}{i 2 \pi \beta C_2 (R_1 + R_2) + 1}$$

$$\frac{v_0'}{v_0} = \frac{1+i[f|g_1)}{1+i[f|f_0)}$$

\* Assuming that the compensating n/w does not load the amplifies.

R2DDR, then overall transfer function becomes

$$A' = \frac{V_0'}{V_1'} = \frac{V_0'}{V_0} \cdot \frac{V_0}{V_1'} = A \cdot \frac{R_2}{R_1 + R_2} \left[ \frac{1 + j(\beta | \beta_1)}{1 + j(\beta | \beta_0)} \right]$$

$$A' = \frac{A_{01}}{(1+i818,)(1+i818_2)(1+i818_3)} \cdot \frac{R_2}{R_1+R_2} \left[ \frac{1+i1818_1}{1+i(818_0)} \right]$$

$$A' = \frac{A \cdot 2}{(1+ifle_0)(1+ifle_2)(1+ifle_3)} \begin{bmatrix} \frac{R_2}{R_1+R_2} & \frac{21}{R_1+R_2} \\ \frac{R_2}{R_1+R_2} & \frac{21}{R_1+R_2} \end{bmatrix}$$

Let  $R_1 >> R_1$ , Such that  $\frac{R_2}{R_1+R_2} \sim 1$

\* consider the frequency response for uncompensated op Amp having three poles at frequencies f, f, f, f3

\* Select R, & C2 Such that 3000 of compensating n/w is equal to pole at freq. f1

\*The pole at to should be selected such that -2001B/decade

fall should meet the odB line at to which is second

pole of A.

gain 1

\* comparison of alominant pole and pole zero technique,

3dB Bardwidth improvement.

\* features of op-Amp:

- · High differential vollage gain

- · low common made gain

- · High CMRR

- · Two ip terminals

- · large B.W

- · low offset voltage & currents

- · low of p impedance.

\* It the base current for the emilter coupled transistor of differential ampr are 1841A & 224A. Détermine (6) Apput bias currents.

is Input offset current for an op-amp

The two input base currents are

i, Input bias current

$$J_b = J_{b,+} J_{b_2} = \frac{18+22}{2} = 2011A$$

ii, Input offset current Iro = | Ib, - Ib2 | = |18-22 | = 44A.

\* for a particular op-Amp the flp offset current is 200A while ilp bias current is 60nA. calculate the values of two phias currents

$$IB = I_{b_1} + I_{b_2} = 60 \Rightarrow 120 = I_{b_1} + I_{b_2}$$

$$T_{b_1} - T_{b_2} = 20$$

$T_{b_1} + R_{b_2} = 120$

$T_{b_1} = 140$

## PROBLEMS

+ The ilp signal Vi to an op-amp is 0.045:n1=13x10=+ is to be amplified to the maximum extent How much maximum gain can be obtained by using op-amp with slew gate of 0.4 V/usec

sol Given input compared with

Vi= Vmsinut

Vi = 0.04 Sin 1.13 x105+

.. Vm = 0.04

10= 1.13 ×105

Also Im = 5R - 1

w= 211fm. => 1.13 x10 = 211fm

Jm= 1.13×10, - (2)

Equating Egn (1, & (2)

$= \frac{1.13 \times 10^5}{2 \text{ m}}$

Given SR= 0.4 V/use c

$\frac{0.4}{10^{-6}}$  = 1.13×10<sup>-5</sup>

$... Vm = \frac{0.4 \times 10^6}{1.13 \times 10^5} = 3.54 V$

This is magnitude of olp voltage Gain = Vmlolp)

Vmlilp)

Gain = 3.54 = 88.5 + In 91esponse to squage wave ilp the olp of an op-Amp changed from - 3v to +3v over a time period of 0.25 US Delermine the slew grate of an op-Amp.

sol change in output voltage -3v to +3v

\* How fast can the output of op-Amp change by 100 is its slew rate is IV/R18?

$$3 = 1 \text{ V/us} = \frac{1}{1 \times 10^{-6}} = 1 \times 10^{6} \text{ V/s}$$

.. Thus 10 usec is nequired by an op-amp

to change output by 10v.

\* For an op-Amp, psrR= todBlmin) CMRR=105 & differential node gain Ad=105. The oip vollage changes by 20v in Allsec calculate

is Numerical value of PSRR

il. common-Mode gain

iii, 81ew Rate.

801 PSRR must be as small as possible

-to = 20 log, o PSRR.

PSRR = 10(-3.5)

= 8.1622 × 10 4 V / vol5

= 31.622 mv/volts

(ii)

$$\frac{Ad}{Ac}$$

= CMRR

$\frac{10^5}{Ac}$  =  $\frac{10^5}{Ac}$  =>  $A_c = 1$

8 lew 9rate =

$$\frac{\Delta V_0}{\Delta t} = \frac{20}{4 \times 10^{-6}}$$

"for an op-Amp. Icq= 15&11 and c=35pf the peak value of ilp is 12v. Determine slew 9ate and maximum possible frequency of ilp voltage that can be applied to get undistorted olp.

30) Imaz = Icq = 15MA

C= 35Pf, Vm = 12V

Slew 9ate SA : 100 1 15 x 106 35 x 10-12

= 0.4285 × 10 V/ sec

= 0.43 V/ wsec

Sm = SR = 0.4285×106

211×12

= 5.684 KHZ

upto this frequency olp is distorted

\* An op-Amp has a differential gain of gods and CHER of 95dB. Is v,= 2ev & v,= 1.6 ev -then calculate the differential and common made output values. Given Ad = BOOB & CMRR = 950B V, = 24V & V, = 1.6 4V -Ad (18) = 20 log Ad 4 80 = 20 log Ad .. Ad = 104 CHRR (dB) = 20 log CHRR 95 : 20 log CMRR . . CHRR = 5.62 × 10+ Differential voltage gain -Ad = Vod = Vod Vid (V, -V2) Vod = Ad (V, -V2) => Vd = 1×10 (2-1.6) × 106 Vod = 4 mv common mode voltage gain Acm = Vocm = Vocm

Viem = Vocm

Viem = Vocm

View = Vocm Also CMRR = Ad => 5.62×104 = 104

Acm Acm Acm = 0.1778

... Voum = 0.1778 × [2+1.6] x10 => Voum = 0.32 uv.

\*Modes of operations:

· Open loop op amp configuration:-

The term open loop indicates that no connection either direct con another now. Exist blue the olp and ilp. i.e. the output signal is not fedback to input signal.

\*In open loop configuration the op-amp simply function as a high gain amplifies. There are three types of open loop op-Amp configurations.

is Differential Amplifier

iis Investing Amplifier

iii, Non-Inverting Amplifier.

\* These configuration are classified according to the number of inputs used.

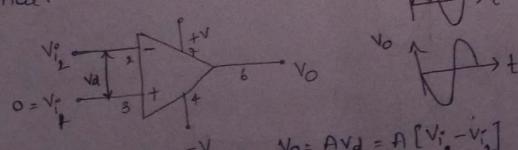

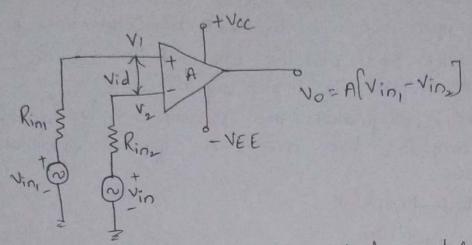

\* Differential Amplifies:

In this the input vin, & vinz are applied to the tre & -re ilp terminals. Since the op-amp amplifiers the difference between the two ilp signals. This configuration is called as the Differential amplifier.

\*The op-amp is a versatile device because it amplifies both ac & dc input signals. That means the Vin, & Vinz Could be either ac or dc voltages.

\*The source 9iesistances Rin, & Rinz are normally neglible negligible compared to the ilp 9iesistance Ri.

.. The vollage drop across the gresistors can be assumed to be zero which then implies that

V = Vin & V2 = Vin2

then Vo = A Vid = A[V\_1-V\_2] => A[Vin, -Vin\_2] = Vo

\* the old voltage is equal to the voltage gain A times the difference blue two ild voltages. And the polarity of the old voltage is dependent on the polarity of the

the OID Switches via

difference Vol. [Vin, - Vin, ] In open loop configuration gain

A is commonly seferred as open loop gain.

open loop Differential Amplifier.

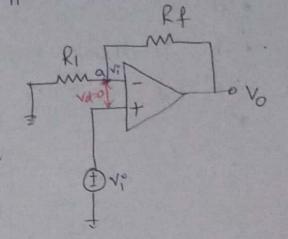

ii, Investing Amplifier:

In the inverting Amplifier only one ilp is applied and that is to the inverting ilp. The non inverting ilp terminal is grounded.

Inverting Amplifies.

Since V1=0 V2=Vin V0=A[Vin, -Vinz] =A[0-Vinz] [V0=-AVin]

\*The -ve sign indicates that the olp votal voltage is out of phase worto ilp by 180° or is of opposite polarity.

\*Thus in investing Amplifier the input signal is amplified by gain A and is also inverted at the output.

\* Non- Inverting Amplifier !-

In this the TIP is applied to the non-inverting TIP terminal and the inverting terminal is connected to ground.

Vialing -VEE TO VO = AVIN

ν<sub>1</sub> = Vin , ν<sub>2</sub> = ον ν<sub>0</sub> = Α[νin, - νin, ] ν<sub>0</sub> = Α[νin - ο]

No = AVIN => A = VO Vin

\* the olp voltage is larger than the ilp voltage by gain 'A' i.e is in-phase with the ilp signal.

only slightly greater than zero drives the olp to saturation level. This result from the very high gain (A) of the op-Amp thus when operated open loop the olp of the op-Amp is either the or -ve saturation (or) switches blue the que saturation levels.

not used in linear applications But used in the

voltage comparator, 3ego crossing detector.

open loop configuration of op-amp may increase the

distortion as well as clipping of olp signal Due to this seasons the olp switches blue the & -ve saturation levels

closed loop means -there is a blue the olp and the ilp terminals through the devices In this we have the feedback and -ve feedback.

4 The gain of the op-Amp is very high in many application Due to that gain the opamp becomes unstable. Gain may be Reduced to any desired value through the use of negative -Peedback.

#II the signal is fed back to opposite polarity (or) out of phase by 180° & w.r.t the ilp signal, the feedback is called

negative leedback

\*An op-amp with -ve Alb has a self correcting ability against any change in olp vollage caused by change in environmental conditions.

\* Negative 1/6 is also called as degenerative 1/6 because when used it reduces the old voltage amplitude and

in turn reduces the voltage gain.

\* If the signal fedback in phase with the ilp signal the SID is called the SIB. It is called as negenerative Sio Slb.

- \* when -ve flb is used in Amplifier then it stabilizes on Reduces the gain, increases the B.W. and changes the flp and olp hesistances.

- . It decreases the distortion.

- . It reduces the obliset of i

- . It reduces the effect of ilp offset vollage at the olp.

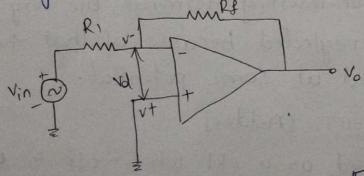

The olp voltage is fed back to investing ilp terminal

through Rg. feedback gesistance

\* The ilp Signal Vi is applied to the inverting ilp terminal

through Ri, ilp gesistance & non-inverting ilp terminal

of op-amp is grounded.

Analysis:

Assume ideal Vi ill present the inverting ilp terminal

op-amp vd=0

From virtual Ground va=vb=0

En product to inverting ilp terminal

ilp terminal

of op-amp is grounded.

Ri

Vi ill present the inverting ilp terminal

of op-amp is grounded.

Ri

Vi ill present the inverting ilp terminal

of op-amp is grounded.

Ri

Vi ill present the inverting ilp terminal

of op-amp is grounded.

Ri

Vi ill present the inverting ilp terminal

of op-amp is grounded.

Apply KVL at node a, we have

$$\frac{N_1^2 - V_0}{R_1} = \frac{V_0 - V_0}{R_g}$$

Va voltage at rode à is zelo

$$V_0 = -\frac{Rg}{Ri} \cdot V_i$$

\*The -ve sign indicates a phase shift of 180° blus N; & Vo. the value of R, should be large to avoid loading effect.

A load resistor Rz is connected at olp to

\* Non- Moverting Amplifier:

If a signal applied to non-inverting ilp terminal & feed back given through the feedback nesistance, the ckt amplifies without investing the ilp signal Buch ext is called non-inverting Amplifier.

\* This is also called as negative feedback system as ofp is being leedback to investing ilp terminal.

· As differential voltage vd=0 at "a' is va=v: (By virtual ground) = Right ovo Rf & R, from potential divider. Voltage at node a.

$$V_a = V_i = \frac{R_i}{R_i + R_g} \cdot V_o$$

$$\frac{V_o}{V_i^o} = \frac{R_i + R_g}{R_i} \Rightarrow \frac{V_o}{V_i^o} = 1 + \frac{R_g}{R_i}$$

Gain of non-inverting amplifier

\* The gain to be adjusted to unity by proper selection of resistors Rg & R, As compared to investing amplifier the ilp resistance of non inverting opamp is large as op-Amp draws negligible current Irom Signal Source.

+ Voltage follower: - (01) Buffer Amplifier.

\*In voltage follower the olp voltage follows the ilp voltage i.e Vout = Vin . The olp voltage is same as ilp voltage both in magnitude & phase.

\* This offers the unity gain because of its high ! Ip impedance and low olp impedance.

\* It is a special case of non-inverting amplifier.

· \* The feedback gesislance Rg=0 and Ri= 10 10e get vollage follower ckt.

Ri=0 Pg=0 Vo

\* feedback gain of non investing Amplifier is

AS = 1+ RA R.

But in vollage follower R,=10, Rg=0.

A8 = 1+ 0 => [A8 = 1] => A8 = \frac{\nabla\_0}{\nabla\_{in}} =1

Athus voltage follower used as buffer for impedance matching (i.e) to connect high impedance source to low impedance load.

## UNIT-11

\* An op-Amp forms the basic building blocks of linear & non-linear analog systems.

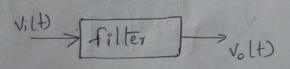

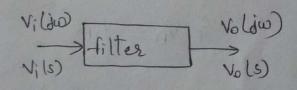

\* linear ckts: output signal varies with the input signal in

linear manner.

Ex: Adder, subtractor, voltage to - current converter, current to voltage conventer, power amplifier etc.,

\* Non-Linear ckts: - output signal varies with the input signal

in non linear manner. Ex: Rectifier, peak detector, clipper, clamper, sample & hold cht, log & antilog amplifier, Multiplier and divider etc.

\* concept of virtual ground:-

\* OP-Amp of open loop gain is very large 105 to 106.

\* consider inverting amplifier. the Input is given to the inverting terminal of op-amp. The -ve flb is considered.

Assume open loop gain Aor = 10%. consider Ve= 10 [Because due to -ve flb the olp

Voltage is less saturates]

Vout = AVd. 10 = 10 Vd

Vd = 10 ev The Vd is less it can be similar to zero VA = OV

V+- V- = 10 MV

terminal are at same potential or it is called as Vistual short blue the inverting and non-investing terminal \* That means the two terminals are not actually short circuited but they are virtually short circuited the Voltage at one terminal appears exactly same at the other terminal.

V+=0 & V=0.

Virtual ground.

\* This -ve flb will ensure that the difference blue inverting and non-inverting terminal are very small and it can be neglected because of that two terminal, can be considered at same potential.

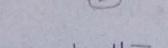

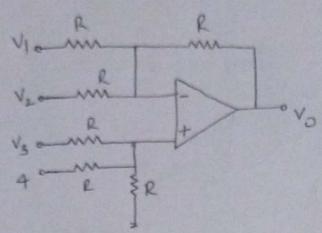

\* summing Amplifier: - (Adder).

op-Amp designed as a ckt whose olp is some sum of several ilp signals such ckt is called as summing Amplifies.

\* Based on the ilp's applied it can be classified in two types.

i, Investing summer

ii, Non-Inverting summer.

\* Inverting Summer:

· A Summing amplifies comprise of three input vollages  $V_1$ ,  $V_2$  &  $V_3$ . Three ilp sesistance  $R_1$ ,  $R_2$  &  $R_3$  and

\* vollage at node a is selo as non-inverting ilp terminal is grounded.

from virtual ground concept vb=va=0.

Apply Kel at node a

$$\frac{V_{1}-V_{0}}{R_{1}} + \frac{V_{2}-V_{0}}{R_{2}} + \frac{V_{3}-V_{0}}{R_{3}} = \frac{V_{0}-V_{0}}{R_{5}}$$

$$\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}} = -\frac{V_{0}}{R_{5}}$$

$$[ \cdot : V_{0}=0 ]$$

Thus the olp is an inverted, weighted Sum of ilpsi for  $R_1 = R_2 = R_3 = R_4$ .

Suppose  $R_1 \neq R_2 \neq R_3$  then  $\frac{R_3}{R_1} \neq \frac{R_3}{R_2} \neq \frac{R_3}{R_3}$

\*In this case along with addition we can also perform scaling operation.

$$A = \frac{Rs}{R_1}$$

,  $B = \frac{Rs}{R_2}$ ,  $C = \frac{Rs}{R_3}$  ... A.B. c are scaling.

factor.

\* The OIP vo is inverted sum of ilp signals for

$$R_1 = R_2 = R_3 = 3R_3.$$

$$V_0 = -\left[ \frac{V_1 + V_2 + V_3}{3} \right].$$

olp is average of ilp signals. So ckt acts as on average.

\* Applications

· Summing, Scaling, Averaging

· providing De offset.

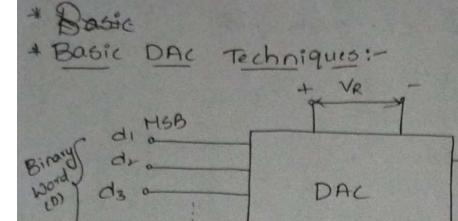

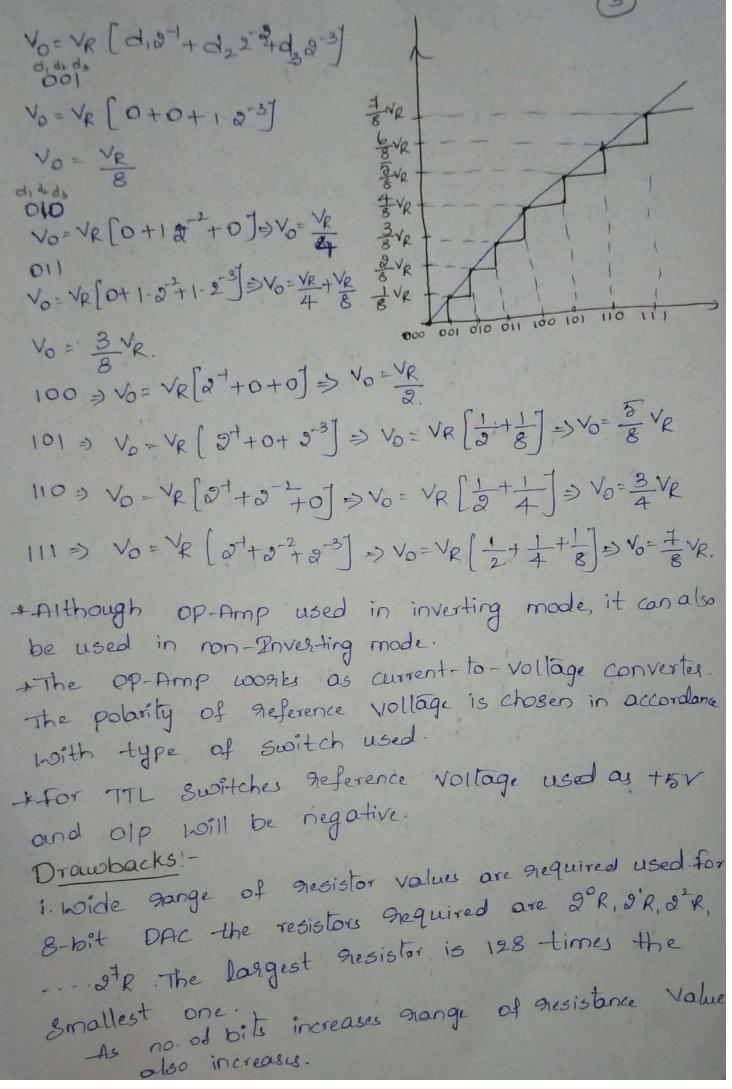

· Digital to Analog converter.

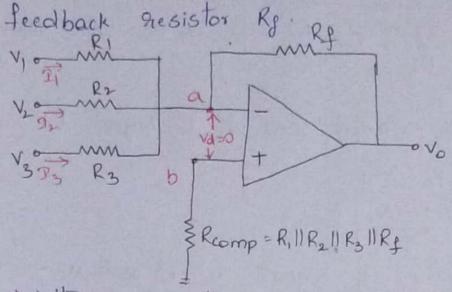

+ Non-Inverting summing Amplifies: (Addes)

· A summer that gives non-inverting sum is called non-inverting summing camplifies. The ilp are applied to the non-inverting terminal of the op-amp:

\* Voltage at non-inverting terminal is va.

-from virtual ground concept voltage at inverting

-terminal is va.

-Apply kel at rode a

$$\frac{V_{1}-V_{0}}{R_{1}}+\frac{V_{2}-V_{0}}{R_{2}}+\frac{V_{3}-V_{0}}{R_{3}}=0$$

$$\frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3} = V_0 \left[ \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} \right]$$

\* Gain of non-Inverting amplifier with Ry & R given as

Sub. value of vo, we get

the olp is the mon-weighted sum non-inverted weighted sum of ilp's : for R1=R2=R3=R=R8 then

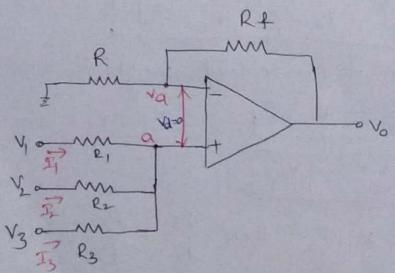

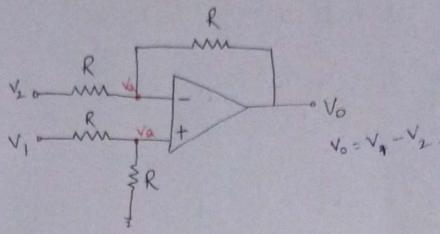

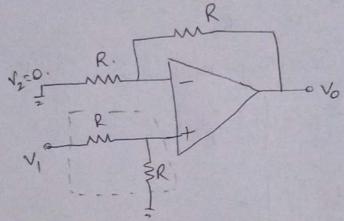

## \* Subtractor :-

The basic differential amplifies used as subtractor, Producing difference of two input signals.

Subtractor.

If all the sesistors are equal in value, then old voltage dervied by using superposition painciple.

· Vo, - output due to v, alone with v=0

At Tapply voltage divides is formed V, x R:

V, x R => V,

the ckt turns into non-inverting amplifier with ilp vollage vi= 4/2 applied at non-inverting terminal.

Gain of ron-in · output voltage Vo1 = V1 [1+ R] Au 10 - (1+ 8) Vo, = V, Vo = V' [ ] + P + Voz- olp due to V2 alone with V,=0 The ckt turns into inverting amplifies with ilp Vollage V2=Vi applied at inverting terminal. Gain of myesting any .. output vollage ALL VO = - PE Vo2 = - V2. \* The output vollage due to No = - 88 V9 the both inputs. Yo = - 8 . Ve Vo = Vo, + Vo2. .. Vo1 = V, ; Vo, = -V, Vo = V1 - V2

\* Adder - Subtractor :-

A single op-Amp ckt can be used to perform addition and subtraction simulation

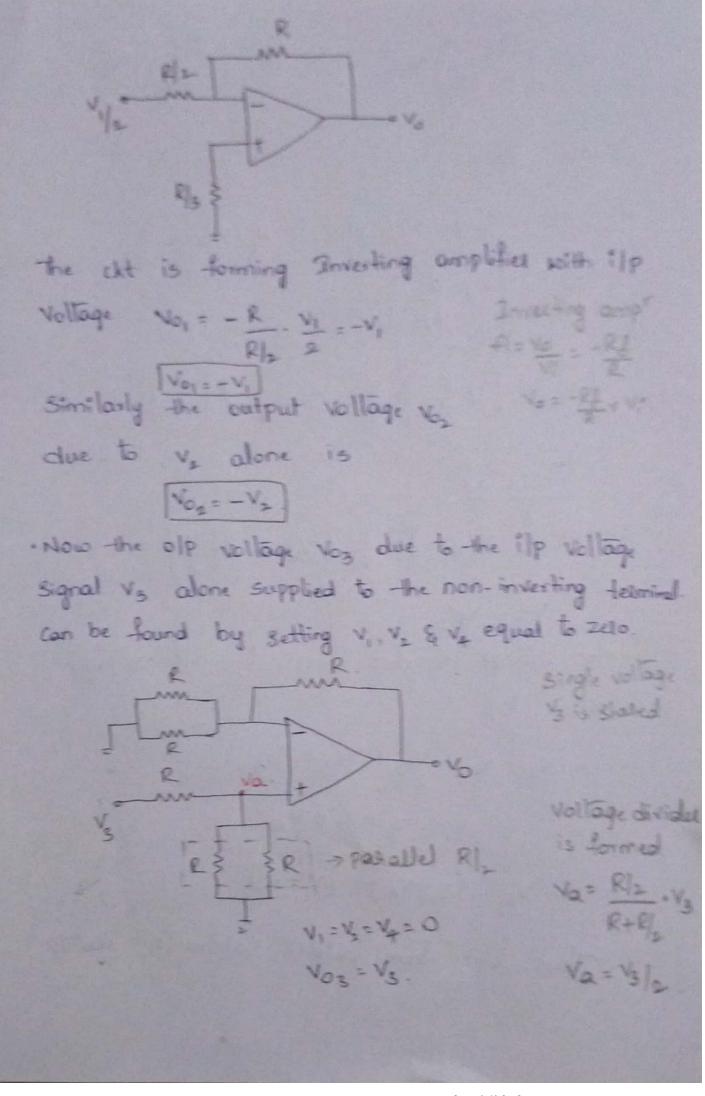

\* the olp vollage vo can be obtained by using Superposition principle.

Voi - old voltage due to vi alone with V2 = V3 = V4 = 0.

Voz - olp voltage due to vz alone with vz=vz=vz=0.

Voz - olp voltage due to vz alone with vz=vz=vz=0

Voz - olp voltage due to vz alone with vz=vz=vz=0

single voltage v, is shared by 2

nesistors R & R

The voltage

divided is

forming

V, x R

R+R

= V, x R

- v, v

Va =

$$\frac{V_3}{3}$$

.

The old vollage vos due to  $\frac{V_3}{3}$  alone is

$V_{03} = \left[1 + \frac{R}{R|2}\right] V_{03}$

$V_{03} = \left[1 + \frac{R}{R|2}\right] V_{03}$

$V_{03} = \left[1 + \frac{R}{R|2}\right] V_{03}$

$V_{03} = V_{03}$

Similarly  $V_{04} = \left[1 + \frac{R}{R|2}\right] V_{03} = 3\left[\frac{V_4}{3}\right]$

$V_{04} = V_4$

old vollage  $V_{04}$  due to all four ill vollages given by

$V_{0} = V_{01} + V_{02} + V_{03} + V_{04}$

$V_{0} = \left[V_{3} + V_{4}\right] - \left[V_{1} + V_{5}\right]$

Thus  $V_{04} = V_{04} + V_{04} + V_{04}$

Thus  $V_{04} = V_{04} + V_{04} + V_{04}$

$V_{05} = \left[V_{04} + V_{04} + V_{04} + V_{04}\right]$

\* Instrumentation Amplifier:

+ The purpose of Instrumentation - Amplifies is to amplify Very low voltage signal.

\* Basically the instrumentation uses transducers. The

- transducers uses converts one form of energy into another form of energy may be in the form of electrical signals. or non- Electrical.

- \* To measure temperature, humidity etc the transducers converts their physical quantity into electrical form.

- \* Instrumentation amplifier is one kind of differential Amplifier with very high gain and high CMRR.

- \* These amplifiers are used in industrial and consumer applications, one is required to measure and control physical quantities.

Ex: - Control of temperature, humidity, light intensity, water flow etc

- \* These physical quantities are usually measured with the help of transducers.

- \* The output of transducers has to be amplified so that it can drive the indicator on display characteristics.

- \* The important features of an Instrumentation Amplifier:

- · High gain accuracy.

- · High gain stability at low temperature coefficients.

- · High CMRR.

- · High slew nate

- · low Dc offset.

- · High ilp impedance.

- · low of impedance.

\* Monolithic (single chip) instrumentation amplifies asse also available commercially such as AD521, AD524, AD620, AD624 by Analog devices.

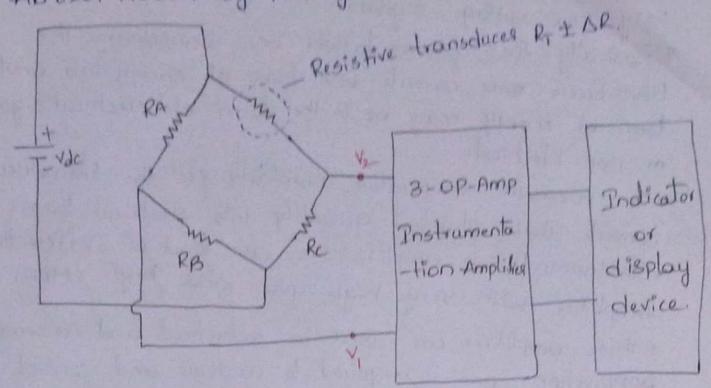

Instrumentation Amplifier using transducer bridge

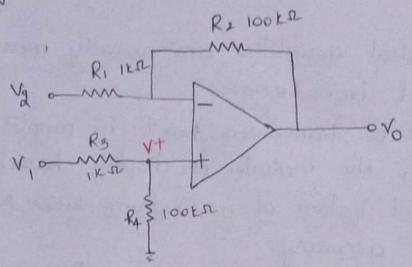

Differential Amplifier using single op Amp.

for basic differential amplifier the old voltage

vo is given by

vo = vo, + vo, [By superposition theorem].

Vo, -s output for v, alone connected with v, is grounded. Vo, -s output for v, alone connected with v, is grounded.

$$V_{01} = \begin{bmatrix} 1 + R_{2} \\ R_{1} \end{bmatrix} V_{1}$$

$$\begin{bmatrix} 4 \text{ from Voltage clivides} \\ V_{02} \end{bmatrix} V_{1}$$

$$\begin{bmatrix} 4 \text{ from Voltage clivides} \\ V_{1} \end{bmatrix} V_{2}$$

$$\begin{bmatrix} 4 \text{ from Voltage clivides} \\ V_{2} \end{bmatrix} V_{1}$$

$$\begin{bmatrix} 4 \text{ from Voltage clivides} \\ V_{2} \end{bmatrix} V_{1}$$

$$\begin{bmatrix} 4 \text{ from Voltage clivides} \\ V_{2} \end{bmatrix} V_{1}$$

$$\begin{bmatrix} 4 \text{ from Voltage clivides} \\ V_{2} \end{bmatrix} V_{1}$$

$$V_{01} = \begin{bmatrix} 1 + R_{2} \\ R_{1} \end{bmatrix} \begin{bmatrix} R_{4} \\ R_{3} + R_{4} \end{bmatrix} V_{1}$$

$$V_{01} = \begin{bmatrix} 1 + R_{2} \\ R_{1} \end{bmatrix} \begin{bmatrix} 1 \\ 1 + R_{2} \\ R_{3} \end{bmatrix} V_{1} - 0$$

$$V_{0} = V_{01} + V_{02}$$

$$V_{0} = \left[1 + \frac{R_{2}}{R_{1}}\right] \left[\frac{1}{1 + \frac{R_{3}}{R_{4}}}\right] V_{1} - \left[\frac{R_{2}}{R_{1}}\right] V_{2}$$

$$= \left(\frac{R_1 + R_2}{R_1}\right) \left(\frac{R_2}{R_1 + R_1}\right) V_1 - \left(\frac{R_2}{R_1}\right) V_2$$

$$=\frac{R_2}{R_1}V_1-\frac{R_2}{R_1}V_2$$

$$V_0 = \frac{R_2}{R_1} \left[ V_1 - V_2 \right]$$

output voltage of a differential amplifier.

PA=R2

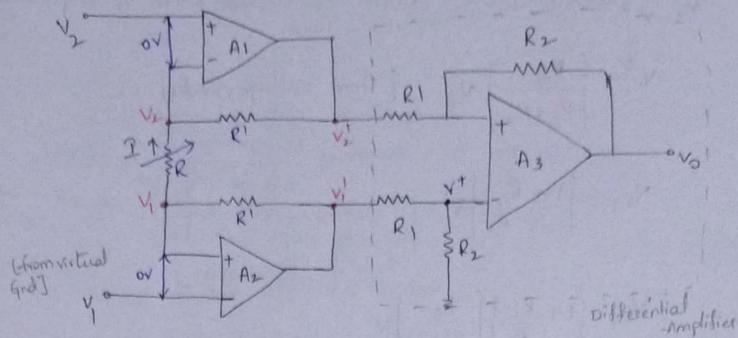

An Improved Instrumentation Amplifier (on Triple op-Amp Instrumentation Amplifier.

\*In the basic differential Amplifier, source V, offeress an ilp impedance Ri= (R3+R4) [:100+1=101xx] and impedance offered by V2 is 1kx.

\* The low ilp impedance loads signal source heavily.

Hence high resistance buffer is used proceeding each

ilp to avoid the loading effect.

\*The op-Amps A, & A, have differential ilp vollage

V\_1=0 for V\_1=V\_2. Under Common-mode condition.

Vollage across R. i.e zero VR=0 [: VR=JR=[V\_1-V\_2]P]

vollage across R. i.e zero VR=0 [: VR=JR=[V\_1-V\_2]P]

As no current flows through R&R' the non-Inverting amplifier A, acts as vollage follower so its

OIP [V2 = V2]

\*Similarly op-Amp -12 acts as voltage follower with olp [v' = v,]

\*But vil v, \$v, turrent flows through RE, R' and [V,'-v,)>[v,-vi] thus cht offers high gain & CHER when compared to single op. Amp.

Analysis'calculation of old voltage

Voltage at 1+> terminal of op-Amp as

$$V^{+} = \left[\frac{R_{2}}{R_{1} + R_{2}}\right] V_{1}^{1} \qquad ; \quad V_{01} = \left[1 + \frac{R_{2}}{R_{1}}\right] V_{1}^{+}$$

$$(for )$$

Using super position theorem

$$V_0 = \left[1 + \frac{R_2}{R_1}\right] V^{\dagger} - \frac{R_2}{R_1} V_2^{\dagger}$$

$$= \left(1 + \frac{R_2}{R_1}\right) \left[\frac{R_2}{R_1 + R_2}\right] V_1' - \frac{R_2}{R_1} V_2'$$

$$= \frac{\left| \frac{R_1 + R_2}{R_1} \right) \left( \frac{R_2}{R_1 + R_2} \right) V_1^{1} - \frac{R_2}{R_1} V_2^{1}}{\left( \frac{R_2}{R_1 + R_2} \right) V_1^{1} - \frac{R_2}{R_1} V_2^{1}}$$

$$V_0 = \frac{R_2}{R_1} v_1' - \frac{R_2}{R_1} v_2' \Rightarrow V_0 = \frac{R_2}{R_1} \left[ v_1' - v_2' \right].$$

\* Since no current flows at ilp side of op-Amp. current I flowing through R is  $I = \left[\frac{V_2 - V_2}{R}\right]$  and passes through R'.

$$V_{3}' = -3R' + V_{3} \Rightarrow -\frac{R'}{R}(V_{1} - V_{2}) + V_{3}$$

Sub. the values of  $V_{1}'$  and  $V_{2}'$  in  $V_{0}$  the old vollage

$$V_{0} = \frac{R_{3}}{R_{1}} \left[ \frac{R'}{R}(V_{1} - V_{2}) + V_{3} + \frac{R'}{R}(V_{1} - V_{2}) - V_{4} \right]$$

$$V_{0} = \frac{R_{3}}{R_{1}} \left[ \frac{2R'}{R}(V_{1} - V_{2}) + (V_{1} - V_{2}) \right]$$

$$V_{0} = \frac{R_{3}}{R_{1}} \left[ \frac{2R'}{R}(V_{1} - V_{2}) + (V_{1} - V_{2}) \right]$$

$$V_{0} = \frac{R_{3}}{R_{1}} \left[ \frac{2R'}{R}(V_{1} - V_{2}) + (V_{1} - V_{2}) \right]$$

\*The difference gain of instrumentational amplifier can be varied by seplacing the resistance R by potentionates.

\*The differential instrumentation amplifier using transducer bridge the ckt uses gesistive transducen tohose gresistance changes as function of physical

\* The bridge is initially balanced by dc supply Vollage Vac such - that V1 = V2.

As the physical quantity changes the gesistance for est transducers also changes causing an unbalance in bridge V, #V2

\*This differential voltage now gets amplified by three op-Amp differential instrumentation amplifier with

\* The applications of instrumentation amplifier with transducer include temperature indicator, temperature controller, light intensity meter etc.

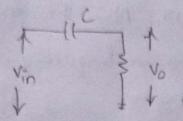

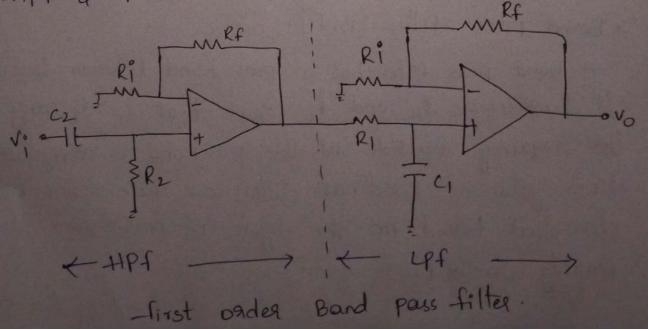

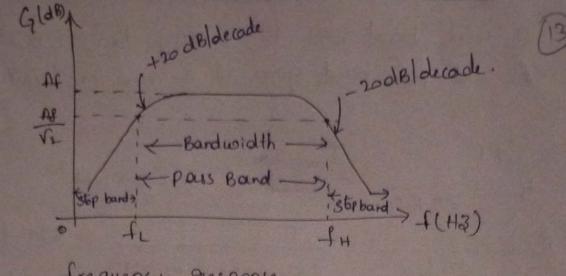

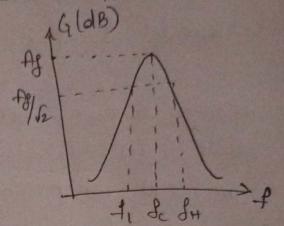

\* Differentiator [HPf]:-

. The differentiator circuit which does not use any active device is called active differentiator.

\*The differentiator ext at which active devices like openmp transistor is called active differentiator.

Apply kcl

$$V_0 = -\frac{Rg}{x_c} \cdot V_{in}$$

$\left[ x_c - 9_{ie} \mu a dance ; x_c = \frac{1}{2\pi g_c} \right]$

The farmer codes and is odbj.

1A1 = \frac{f}{fa}.

At f = fa , 1A1 = 1, i.e od. B & gain increases at state of the odbldec.

\* Thus at high frequencies, differentiated becomes becomes unstable & breaks into oscillations. Also the impedance [xc = \frac{1}{30\text{Tiles}}] decreases with increases in frequency and makes out sensitive to high frequency noise.

+ frequency gesponse of ideal Differentiator: Let us consider olp expression Vo(t) = - Rg (1 d v; (+) Apply L.T on both sides we get. Vols) = - SRg ( Vils) Vols) = - SRg CI To get freq gesponse 5=jw Noliw) = -judg (1 v. Ljus wo is angular frequency = 2114 1A1 = Voldo) = 1-jwRgG1 = To+(wRgG) = wRgG1 1A1 = 217 f R; (1 let da = STRECT Nots) = - R + As freq Ases the Gain 1 gain of differentiator (dB) also increases + But the gain of differentiator cannot 154 e indesinitely & the gain is restricted by the open teop gain of op-Amp. \* 80 the max. gain attainted by the differentiator is the intersection point of differentiator and the open loop gain of op-amp.

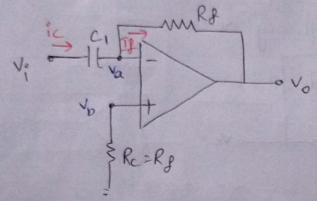

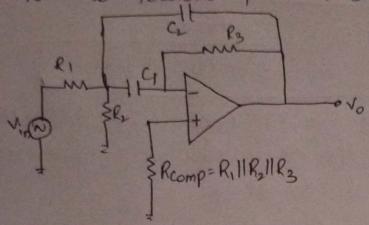

\* Practical Differentiator: The practical differentiator eliminates the problem of Stability and high frequency noise. Vi amilia FRcom= Rilleg \* By the feedback Capacitance Cr we can improve the stability at the output of op-amp. \* Apply kel at node 'a' I1 = I2+ P3 Vin-Va = Va-Vo + Cf of [Va-Vo] R+ 34 :. Va=0 (from virtual ground concept)

$$\frac{V_{n}(t)}{R_{1}+\frac{1}{5}c_{1}} = \frac{-V_{0}(t)}{R_{1}} - c_{1} \frac{d}{dt} V_{0}(t)$$

$$\frac{P_{0}(t)}{R_{1}+\frac{1}{5}c_{1}} = \frac{-V_{0}(t)}{R_{2}} - 3c_{1} V_{0}(t)$$

$$\frac{V_{n}(t)}{R_{1}+\frac{1}{5}c_{1}} = \frac{-V_{0}(t)}{R_{2}} = 3c_{1} V_{0}(t)$$

$$\frac{V_{n}(t)}{R_{1}+\frac{1}{5}c_{1}} = \frac{-V_{0}(t)}{R_{2}} \left[ \frac{1+3c_{1}R_{2}}{R_{2}} \right]$$

$$\frac{V_{0}(t)}{V_{1}(t)} = -\frac{R_{2}}{R_{2}} \frac{c_{1}}{(1+5R_{2}c_{1})} \cdot V_{0}(t)$$

$$\frac{V_{0}(t)}{V_{1}(t)} = -\frac{R_{2}}{R_{2}} \frac{c_{1}}{(1+3R_{2}c_{1})} \left[ \frac{V_{0}(t)}{V_{1}(t)} - \frac{R_{2}}{R_{2}} \frac{c_{1}}{(1+5R_{1}c_{1})^{2}} \right]$$

$$\frac{V_{0}(t)}{V_{1}(t)} = -\frac{1}{2} \omega R_{2} c_{1}$$

al elast Differentialor: Volde) = - 3217 Rg C, v: (jw) (1+j211fR, (1)) fa = 1 211 Rici ii, Rg4>>RG4(Rg4) Vo (jw) = - j (f/8a) VOLS) - - 34 Rg (1+8 \$/86)2 Vo(5) = - Ry C, 5 V; (1) Magnitude Volt) = - Rg C, d V; (+) 1A1 = | voliw) = f/fa. i, consider fa=10f, fb=100f, f=10f 1A1 = 108/108  $\sqrt{1 + (108/1008)^2} = \sqrt{1 + \frac{1}{100}}$ Gain in dB= 20log (A) = 20log (1) = 0dB. Again (dB) Ideal -20d8/decade + 20 alBldecade RodB rockal differentiator 10dB odB fa=1 fo=1 frequency. King.

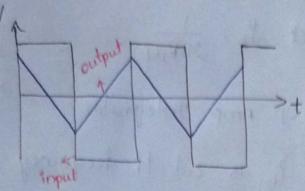

\* As the frequency increases, gain increases till fifth at rate of sodeldecade. -After fifth the gain decreases at the nate of - dodB/decade. \* The gain decreases as trequency increases > 16 Hence the problem of instability at high frequency get eliminated. D d (Vin) = d(1) = 0. The olp of dc ilp signal. 1. squale wave. sine. ilP 360 OIP COS .

oreps to design practical differentiator: is choose fa as the highest freq. of ilp signal [fa= 1 TRg4] in choose of to be < 121f & calculate value of Rg. in, choose is as 10 times to [fb=10fa] [fb= 1 ] iv, calculate the values of Ri & Cf from the expression Rici = Rg Cf. V, Recomp = R, 11Rg. \* Design a differentiator on input signal that varies in freq. from 10H3 to 1KH3 If a sine wave of IV Peak at 1 kH3 is applied to this differentiator. Draw its output waveform. Given freg: 10H3 - 1KH3 C1=14f.  $R_g = \frac{1}{2\pi i J_{\alpha} C_i} \Rightarrow R_g = \frac{1}{2\pi i \times 1 \times 10^3 \times 1 \times 10^5}$ Rg = 15952 fb = 10 fa =) fb = 10 x 1 kH3. 1-16 = 10 kH3. 16 = 1 2TTR, C,

211 XIOK XILL = 15.90 3 R1 = 15.90 Rici = Rici R = 17 x10xx12 = 15.90 RC1 = C1 => Rg = R1 C1 Rg = 15.9 x 1 LL ] x Rici = Rg Cf CF = R, C4

RR Cf = 15.9×14 = 0.14 [: G=0.14f Rc = R, 11Rg = 159/15.9 = 14.452 [: Rc = 14.452 SIP OST \* Application of Differentiator: + It can be used as wave shaping ckt \* Edge detection in fM demodulators \* Aralog computers.

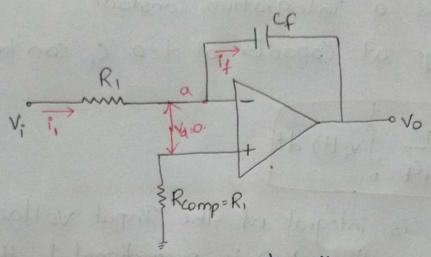

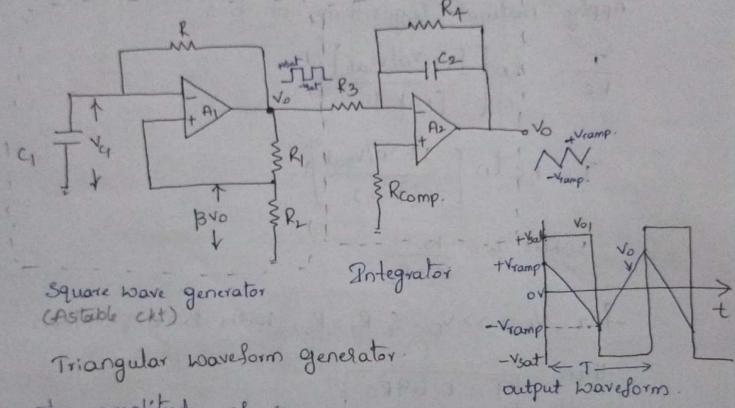

\* Intergator:

. It is also called Integration Amplifier.

· The output voltage is integral of input voltage then the

ciacuit is called Integrator.

\* The interchange of the gresister and capacitor of the differentiator is the integration.

\* From the basic capacitor theory The Vollage developed across the Capacitos and the charging current have relationship.

$$i = c \frac{dv}{dt}$$

-Apply kel at node a

$$\frac{V_i - V_a}{R_i} = C_f \frac{d}{dt} \left( V_a - V_o \right)$$

it is virtual ground.

Where Ci is a integration constant.

\* Initial voltage at Capacitor at t=0 G can be set to Zero.

- output voltage is integral of the Input voltage \* Thus the output vollage (Vo) is proportional to the

integral of input vollage with Ricf as time constant

of integrator.

\* As negative sign indicates inverting Integrator.

\* A gresistance Rcomp = R, is connected to (+) ilp terminal

to minimize the effect of ilp bais current.

\* A simple low pass Re circuit act as integrator when time constant is large (9>>Ric). This Requires large value of R and c. 11)

\* Il the input voltage is constant viev.

i.e The output is a namp.

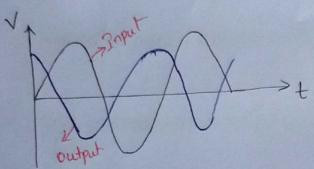

\* for a square wave input we get output as triangular

\* Il input is a sinusoidal signal

Apply laplace Transform on both side

to -Relki [Re=10Ri] providing stability and minimizing the variations in outpute, vollage

\*Analysis:-

Apply kel at node a'

$$\frac{V_i^2 - V_a}{R_i} = C_f \frac{d}{dt} (V_a - V_o) + \frac{V_a - V_o}{R_g}$$

But Va=0 as it is virtual ground.

$$\frac{V_i(t)}{R_i} = -C_f \frac{dV_o^{(t)}}{dt} - \frac{V_o(t)}{R_f}$$

Taking laplace Transform on both sides

$$\frac{V_i(s)}{R_i} = -S(fV_0(s)) - \frac{V_0(s)}{R_f}$$

$$\frac{V_{1}(s)}{R_{1}} = -V_{0}(s) \left[ sc_{1} + \frac{1}{R_{1}} \right]$$

$$\frac{V_{o}(s)}{V_{i}(s)} = -\frac{1}{R_{1}} \left[ \frac{1}{34 + \frac{1}{R_{f}}} \right]$$

for freq. 1> fa gain RJR, is constant, gain decreases at gate of -20dB/decade values of fa, R, G, R, G, Should be chosen.

\*Applications:-

The integrator is used in analog computer & analogto-digital (ADC) and wave shaping circuit. Design a lossy integration using op-Amp so that peak gain is node & gain is 3dB down from its peak value for w=10,000 nad1sec use c=0.014f.

sol HAT Magnitude of gain for lossy integrator given by  $|A1 = \left| \frac{V_0}{V_1^2} \right| = R_2 |R_1|$

V1+(wRgG)2

1Alab = 20 log, [ R8 | R, ] [ \( \tag{1+2718 R3 C3}^2 \)

Gain is at its peak when w=f=0

Peak value in dB given by

(A) dB = 20 log (RS/R) = 20 (Given)

2 d log10 (88/R1) = 26

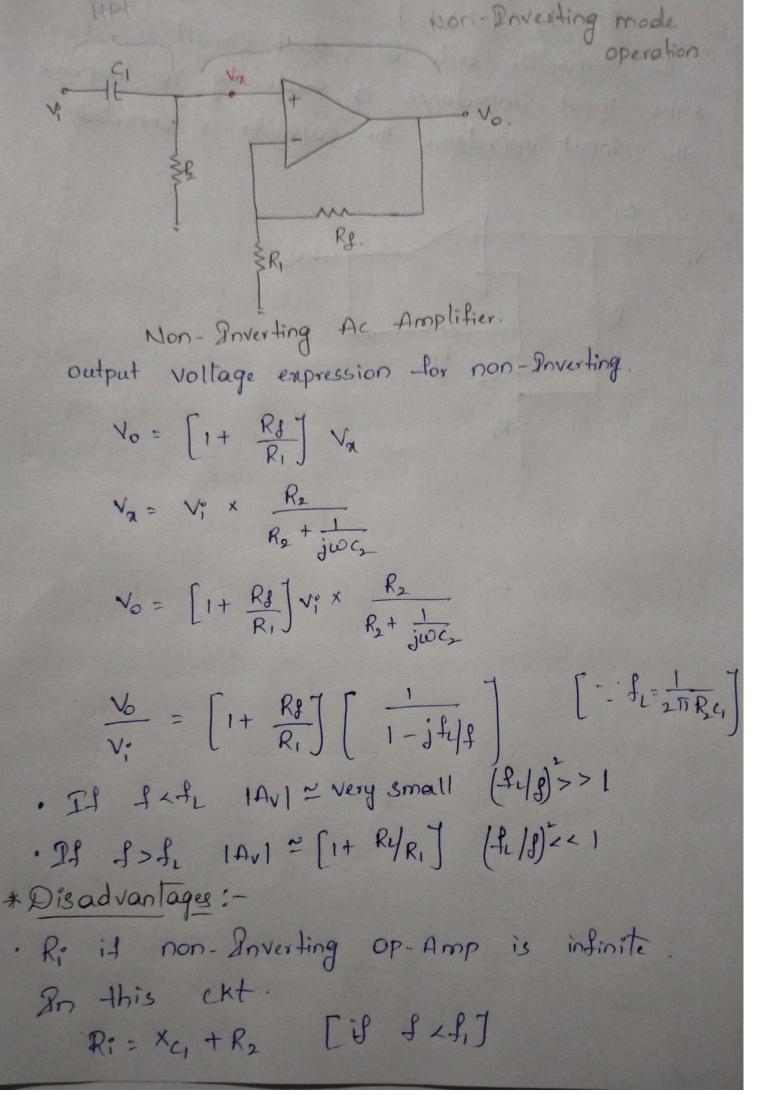

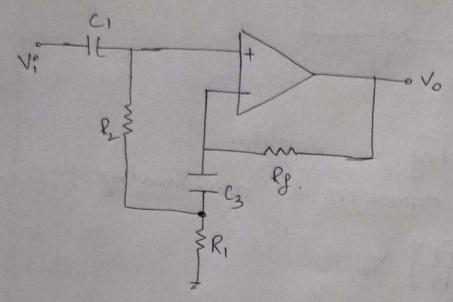

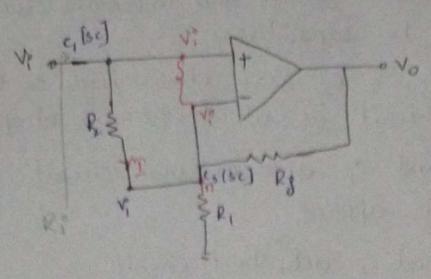

\*Ac Amplifier:

The op-Amp can amplifies both the types of signals. De and the the op-Amp respond to ac signal is called ac Amplifies.

\* Ac amplifier are of two types:

· Inverting Ac amplifier.

· Non. Investing Ac Amplified

\* Inverting Ac Amplifier:

\*The input is provided across the inverting terminal of the op-Amp.

withe capacitor is used to block the de components.

Apply kel at node 'a'

$$\frac{V_i - V_a}{R_i + \frac{1}{3L_i}} = \frac{V_a - V_o}{R_f}$$

$$\frac{V_1^2}{R_1 + \frac{1}{j\omega Q}} = \frac{-V_0}{R_s^2}$$

$$V_0 = -R_f \times \frac{V_i^*}{R_i + 8 \frac{1}{j \omega_{G}}}$$

: Va= 0 [from virtual quo

filter connected to the non- Inverting

terminal.

· R:= R2 [1>f2]

The capacitor acts as short circuit.

\*The input impedance is neducing To improve

the input impedance the capacitor is connected.

· For fl. f. The capacitor c, & c, acts as open

·If C, is open circuit that means no input is transmitted at the non-Investing terminal.

· output is independent of input Vo=0 Even if Vin is applied. It is blocking the dc components

Vin .

\* for f>ti. The capacitors acts c, and c3 acts as short cincuit.

\* The both ends of R2 are of Vo.

\* vollage drop across R2 =0.

$V_{R_2} = IR_2$  =) I = 0.

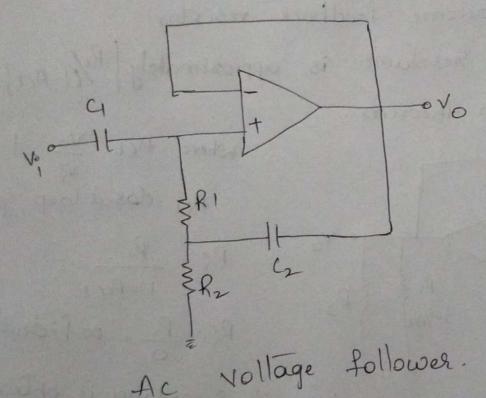

\*Ac voltage follower: - Ac Amplifier with unity gain

· characteristics :-

voltage follower is an ideal voltage

. R:= 10

· Ro = 0

amplifier with unity gain.

\*The circuit is used as a buffer to connect a high impedance signal source to a low impedance load which may even be capacitive.

\* The capacitor of & of are chosen high so that

they are short circuit at all frequencies of operation

\* for Isl. of and of acts as open circuit

Vo = 0 Even vo is applied.

+ for Isli, 4 and 4 acts, short circuit

Because of Vistual short Vo = Vi [Now the circuit is acting as voltage follower].

\* Since G is short circuit

\* Since c2 is acting as short circuit that makes R, to fee become feedback resistor.

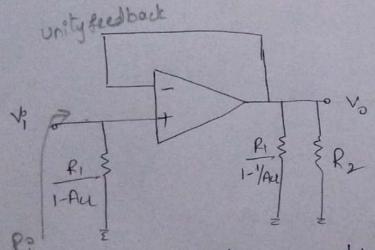

\* The input resistance is approximately [R/LI-Act] from miller's theorem.

where  $Acl = \frac{V_0}{V_i^0} = 1$  Acl = closed loop gain  $R_i^0 = \frac{R_1}{1 - Acl}$   $R_i^0 = \frac{R_1}{0} = \infty. (ideal)$

\* thus very high ilp impedance is obtained

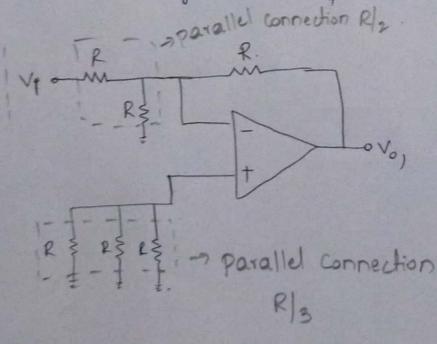

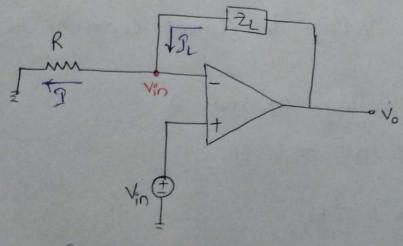

\* Voltage to current converter [Transconductance Amplifier]:

\* The circuit converts an input voltage signal to proportional output current.

\* This circuits are used in Industrial applications and Instrumentation.

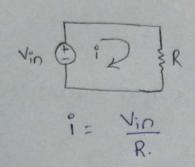

\* consider passive circuit.

. The current is proportional to input voltage

At the Current dependents on the load Resistance also.

\* By using the active component i.e op-amp. There are two types of circuits possible.

is voltage to current converter with floating load.

(ii, Voltage to current converter with grounded load.

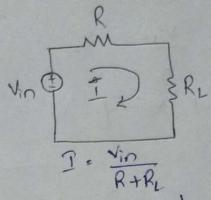

floating load.

\* The ckt shows vollage to current converter in which load Ze is floating.

let v: be vollage at node a' [virtual ground]

$$\frac{V_{in}^{e}}{R} = \Omega_{L} \qquad \qquad \vdots \qquad \Omega_{L} = \frac{V_{in}^{e}}{R}.$$

Input voltage vi is converted into an output current of vi R.

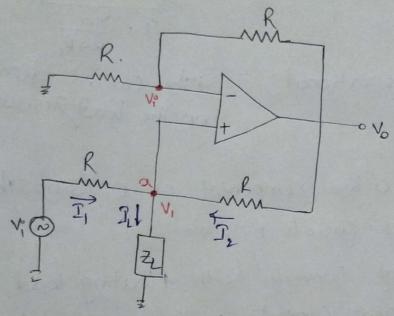

Grounded load.

\*The cht shows voltage to current converter with grounded load.

let v, be vollage at rode a'

Apply kel at node a'

$$\frac{V_{in}-V_{i}}{R}+\frac{V_{o}-V_{i}}{R}=3L$$

Since op-amp is used in non-Inverting mode gain of non-Investing amplifier.

$$A = \frac{v_0}{v_0} = \left(1 + \frac{R_0}{R_1}\right)$$

PL = Vo R. 2t is independent of the load nesistana

\* The application include 1000 voltage de & ac voltmeter, LED and Zener diode tester.

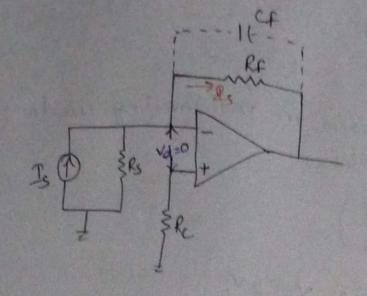

\* current to vollage converter [Transnesistance Amplifies];

\* The devices like photocell, photo diode and photo voltair cell gives an output current proportional to incident hadiation energy on light.

\* The current through these devices can be converted to vollage by using current to vollage converter and hence amount of light or incident gadiant energy measured.

\* The figure shows op-Amp used as current to voltage converter with inverting (-) input terminal at virtual

\* Thus no current flows through Rs & current flows through feedback nesistance Rf.

Hence output vollage [Vo= -28 Rf.]

\* The resistor Rf is shunted with capacitor cf to reduce high frequency noise and possibility of

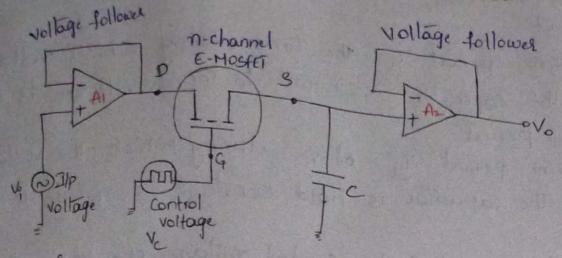

\* Sample and Hold circuit:

\* A sample and Hold circuit samples an input signal and holds on its last sampled value until the input is Sampled again.

\* This type of cincuit is useful in digital interfacing and analog to digital and pulse code modulation systems.

\*The n-channel E-MosfET works as switch and controlled by control voltage ve and capacitor c' stores the charge.

-fig! Sample and Hold cincuit.

\* The analog signal V: to be sampled is applied to drain of MOSFET and control voltage Ve is applied to its gate.

\* operation :-

\* When Ve is positive the E-MOSFET turns on and capacitos 'c' charges to instantaneous value of input vi with time constant

J= [(Ro+9105)(00)] C.

Where Ro is output resistance of the vollage follower

ADS LOW) - Resistance of MOSFET blw drain and source when MoSFET is turned on.

\*Thus the input vollage vi appears across the capacitos is and then at the output through the vollage followers Az.

\* During the time when control voltage Ve is zero the MOSFET turns off. The capacitor 'c' Now connected to high input impedance of voltage follower Az and hence cannot discharges. The capacitor holds the voltage

\* The time period 'T's the time during which voltage across the capacitor is equal to input vollage is called Sample period. \* The Time period 'TH' . of Ve during which the voltage across the capacitor is held constant is called Hold Period. \* the frequency of the control voltage should be kept higher than the input so as to retrive the input from output waveform. Control Vollage of fig: Typical Connection Diagram. \* A typical connection diagram -m of the lf398. It may be noted that the Storage Capacitos c is connected enternally. . Input and output waveforms. During off:-Switch-off, ckts works on Holding made During on switch on, c-charges, ext works on Track mode [sample]

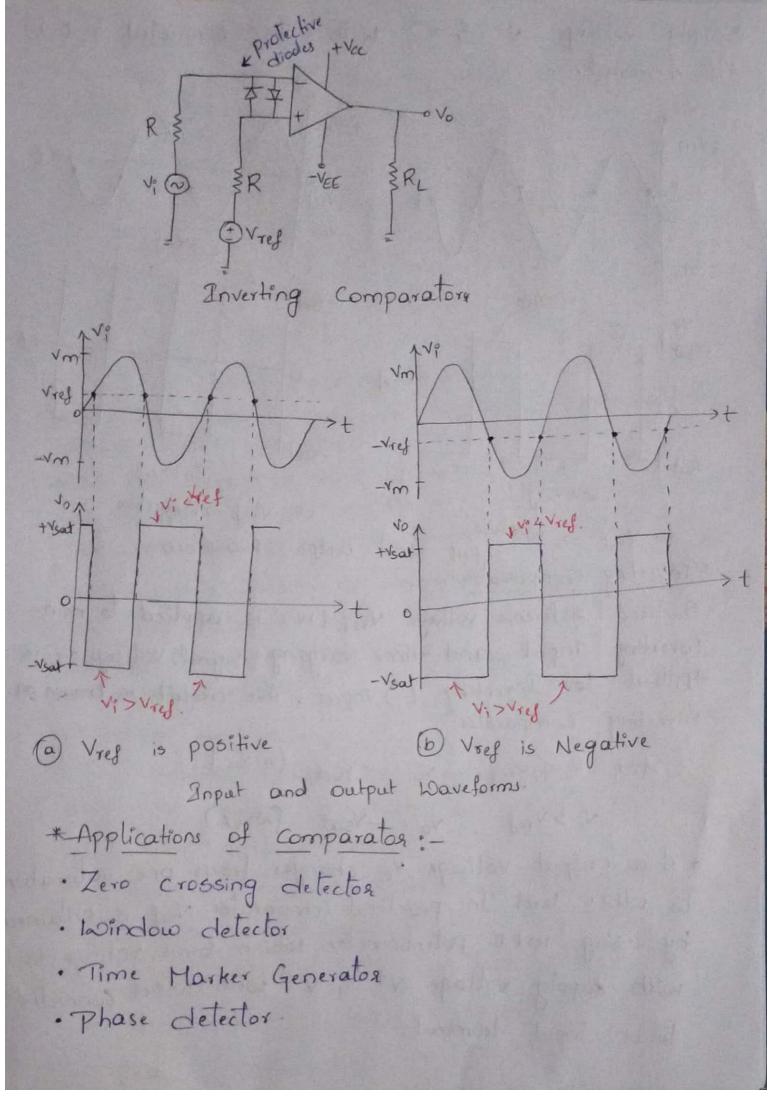

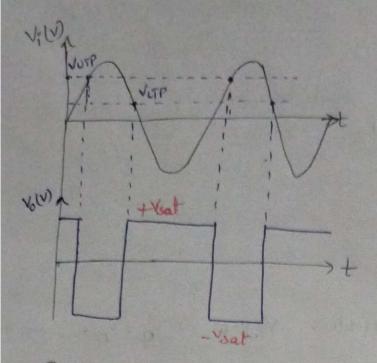

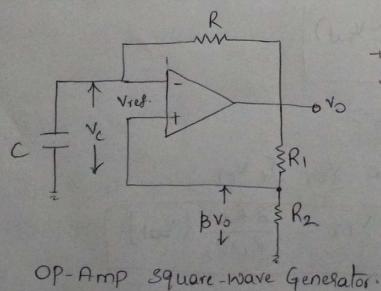

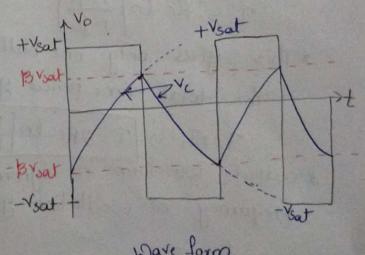

\* Comparator :-

\* The non-linear applications of op-Amp include comparator, detector, limiters, Digital Interfacing etc.

\*A Comparator is a circuit which Compares input signal voltage at one input of an op-Amp. With known Reference voltage at other input.

\* It is basically an open-loop op-Amp with two analog

input and digital output varies ± Vsat

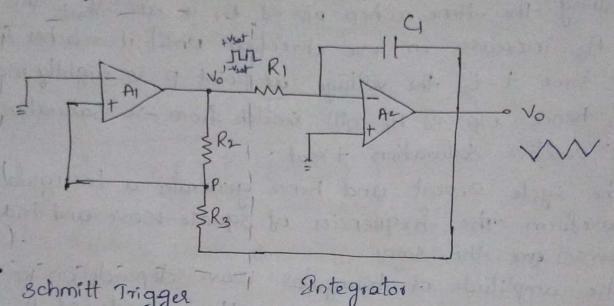

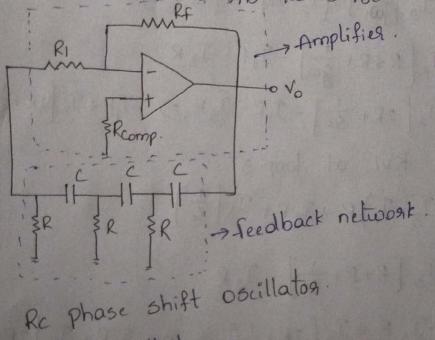

\* These are used in circuits such as digital Interfacing, Schmitt trigger, descriminators, voltage-level detectors and oscillators.

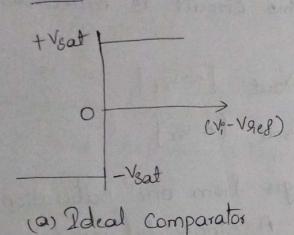

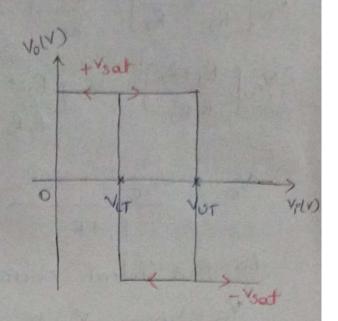

Transfer characteristics

+10V - 10. 1 2 (Vi-Vref)

(b) Practical comparator.

\* There are two types of comparators

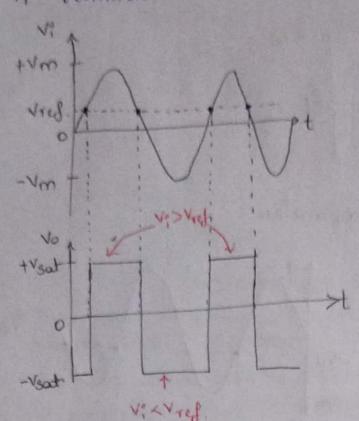

i, Non-Inverting comparator [ V; > Vref -> Vo Switches from ]

-Vsoit to +Vsoit

EVi < Vref -> Vo Switches from

+Vsoit to -Vsoit

ii, Investing comparator.

[ Vi > Vref. -> Vo Switches + Vsat to -Vsat ]

Vi < Vref -> Vo Switches - Vset to + Vsat ]

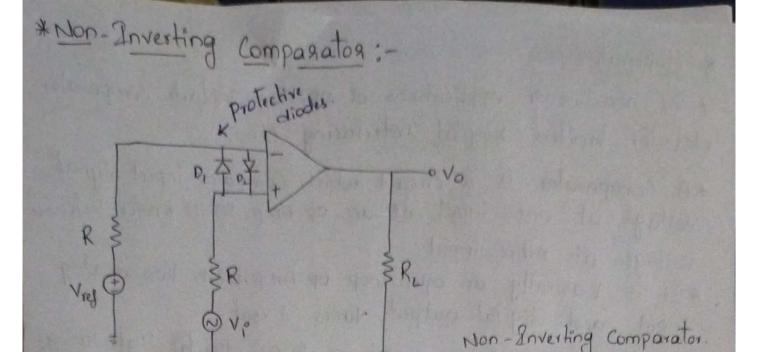

\* A fixed het voltage vies (IV) is applied to Inverting (-) ilp and time varying signal voltage vi is applied to non-Inverting terminal this circuit is called as non-Inverting comparator.

for Vix Vref, Vo = -Vsat [~VEE] Vi>Vref, Vo = +Vsat [~Vcc]

\* Thus of voltage vo changes from one saturation level to another saturation level. A sinusoidal input wave converts into square wave input.

\* The comparator is of analog. to-digital converter.

\* The diodes D, & D. protects the op-Amp from damage due to encess input voltage v. Due to these diodes. The difference ilp voltage Vid of op-Amp is clamped to ±0.7 V. Hence diodes are called clamp diodes.

Vref. obtained by using lown ov; Potentiometer which forms I Voltage divider. with supply vollage v+ & v with wiper connected to 1-)

(b) Vref -> Negative.

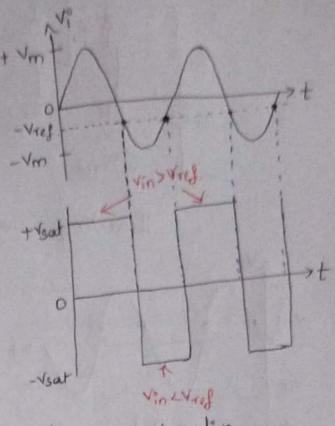

\*Inverting Compagator:-

A fixed reference voltage Vref (IV) is applied to non-Inverting input and time varying signal voltage Vi is applied to Inverting (-) input. This circuit is trouve as Inverting comparator

for vi L Vref, vo = + Veat (~ Vec)

V: > Vred , Vo = - Vsat (NVEE)

\*Thus output vollage vo changes from one saturation to other level. In practical comparator viet is obtained by using 10 ks. potentiometer which forms voltage divides with supply vollage V+ & V with wiper connected to (+) input terminal.

\* Zero Crossing Detector :

The basic comparator can be used as zero crossing delector provided vseg = ov

protective add o+v

Prolection of Vo

Zero crossing Detector.

\* This cht converts sine wave into square wave called square wave generator.

the old wave form, vo driven into motor ve saturation. when ilp vollage vi

Passes through Belo in the direction mit

\* Also olp waveform (vo) driven + Vsat into +ve saturation when ilp of vollage vi passes through Zero - Vsat in -ve direction.

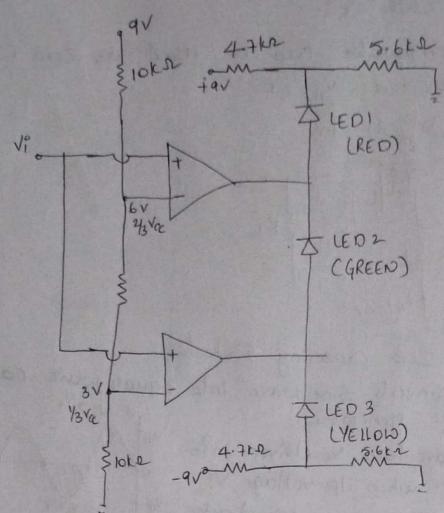

\* Window detector:

\*The window detector is circuit which is used to mark the instant at which an unknown 1/p is blue two threshold levels.

\* A three level detector with three indicator circuit

\* there are three indicator

Yellow (LED3) - ilp too low (23V)

Green (LED2) - sale ilp (3-6V)

Red [LED1] - high ilp (>6V)

Vi LVr, No = + Vsat

Level comparator with Indicator.

Red (LEDI) Input (volts) Yellow (LED3) Green (LED2) 044 off ON less than 3V B/w 34 & 64 off off ON Greater Hantv Off off

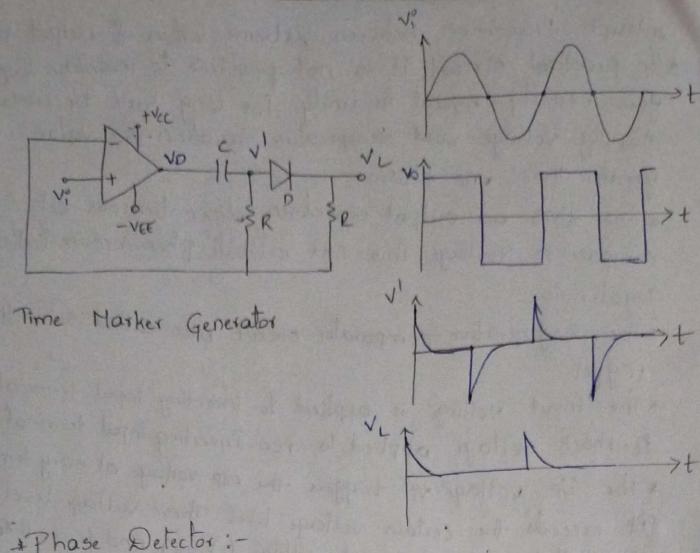

\*Time Marker Generator:-

\* The olp of the Zero crossing detector is differentiated by an RC ckt (RCKKT) such that V' is in Series of

positive negative spikes

\* The negative postion is clipped off after passing through the diode (D). This cxt converts sinusoidal into train of pulses of spacing (T) and used for triggering monostable, scr, sweep voltage of CRT etc.

+ Phase Detector: -

\*The phase angle 1010 two voltages can be measured Using time marker generator Both voltages are converted into spikes and time interval blue pulse spikes of one ilp and that of other is measured.

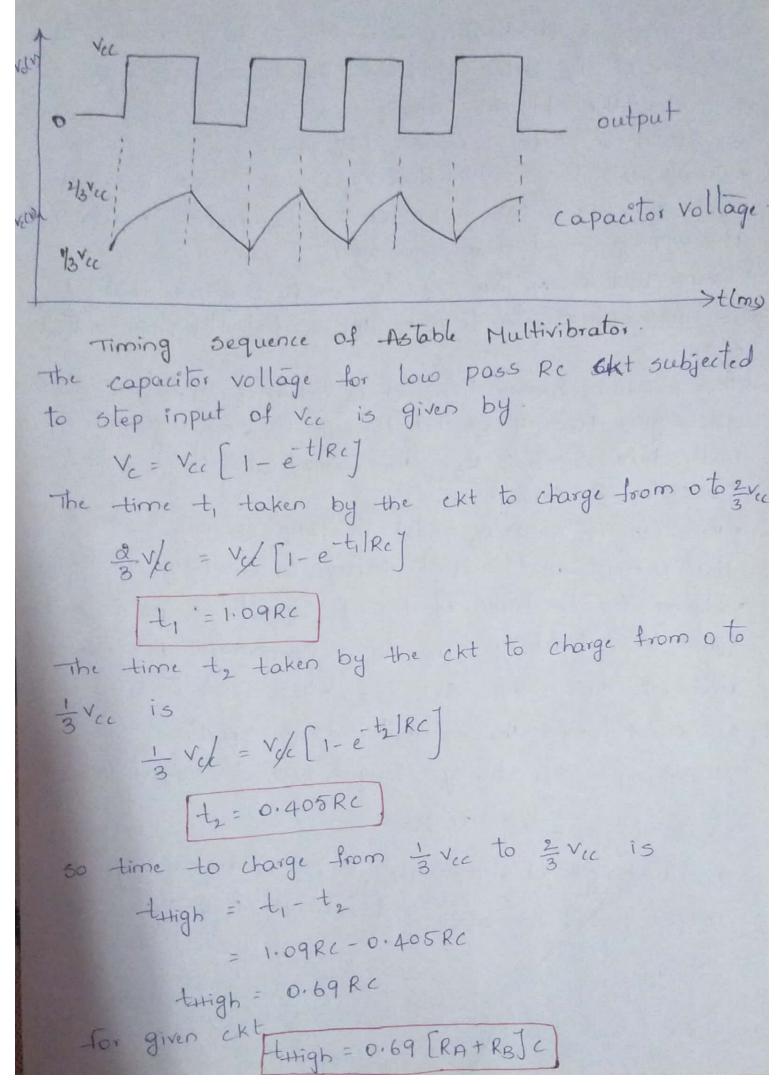

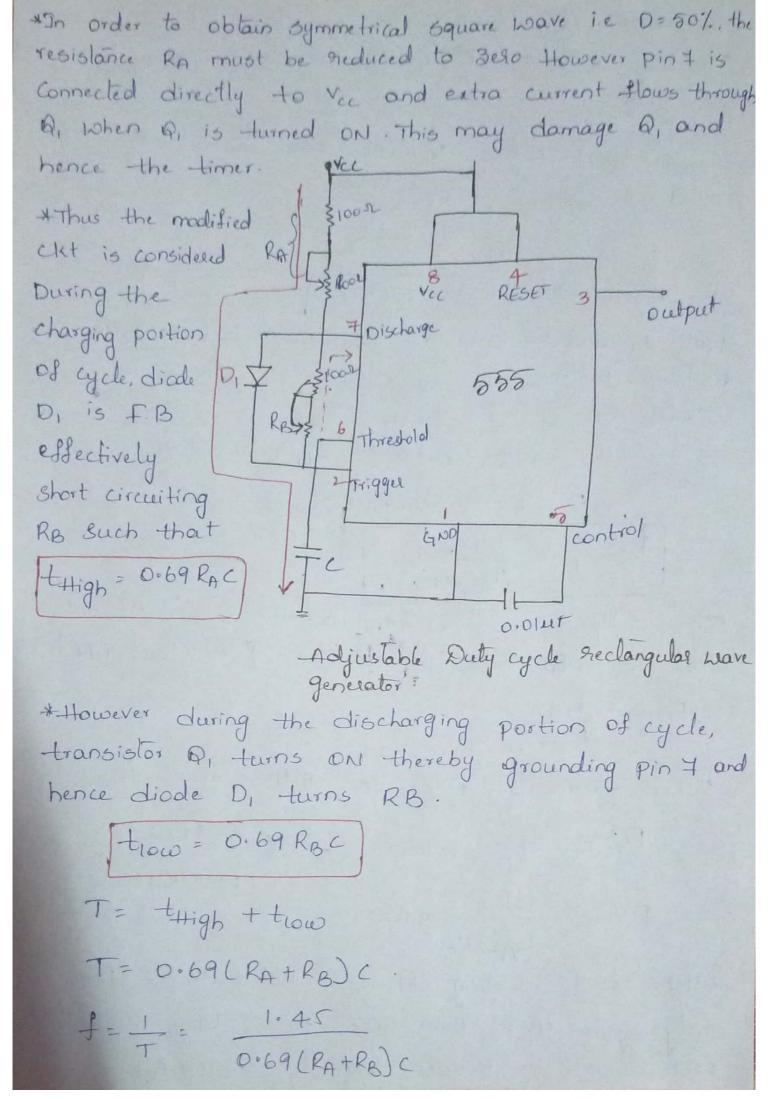

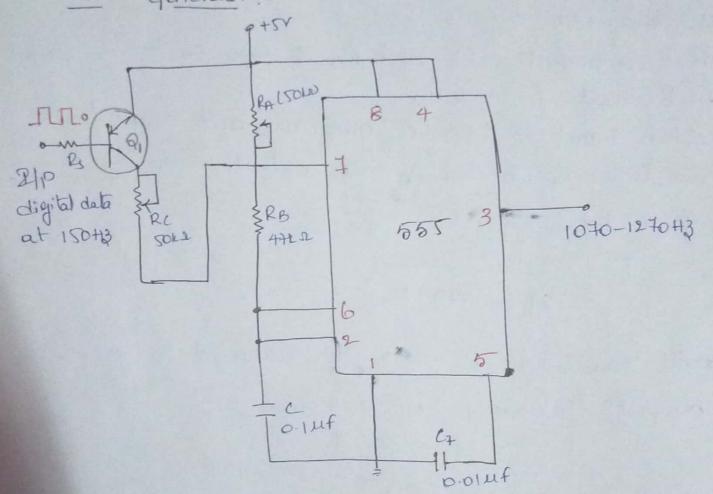

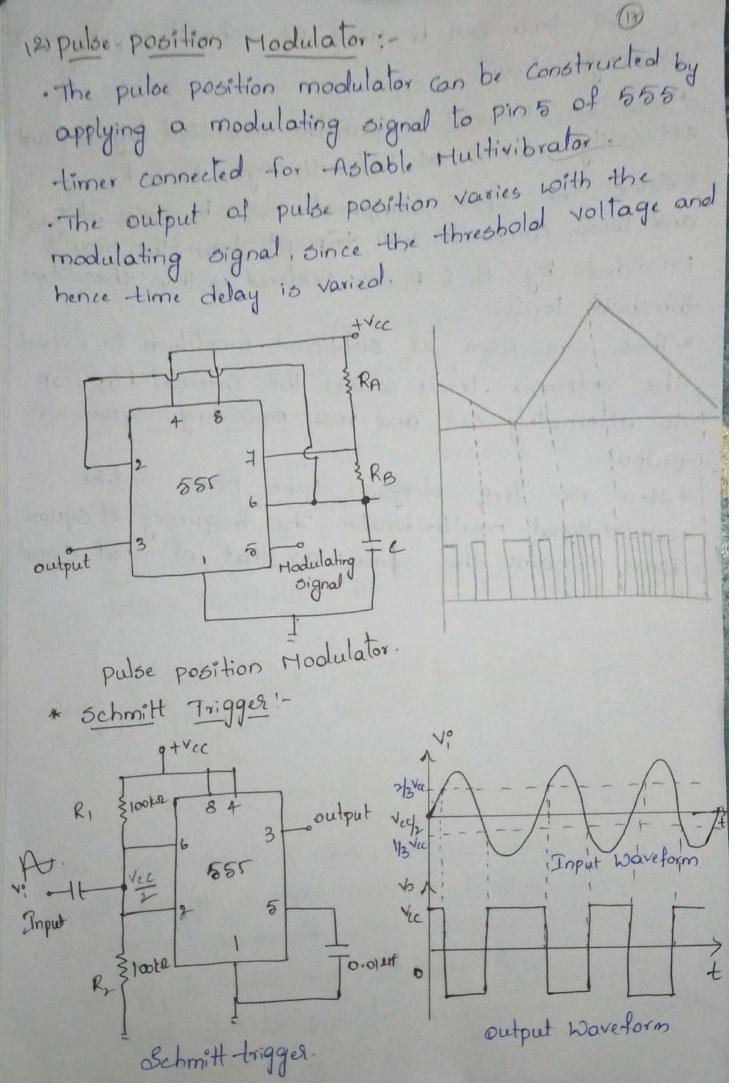

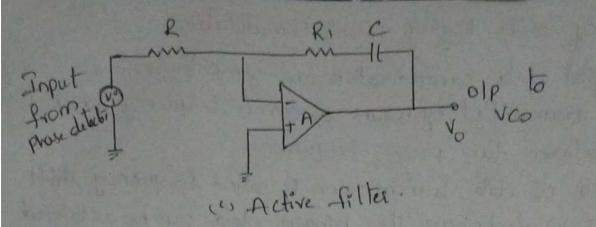

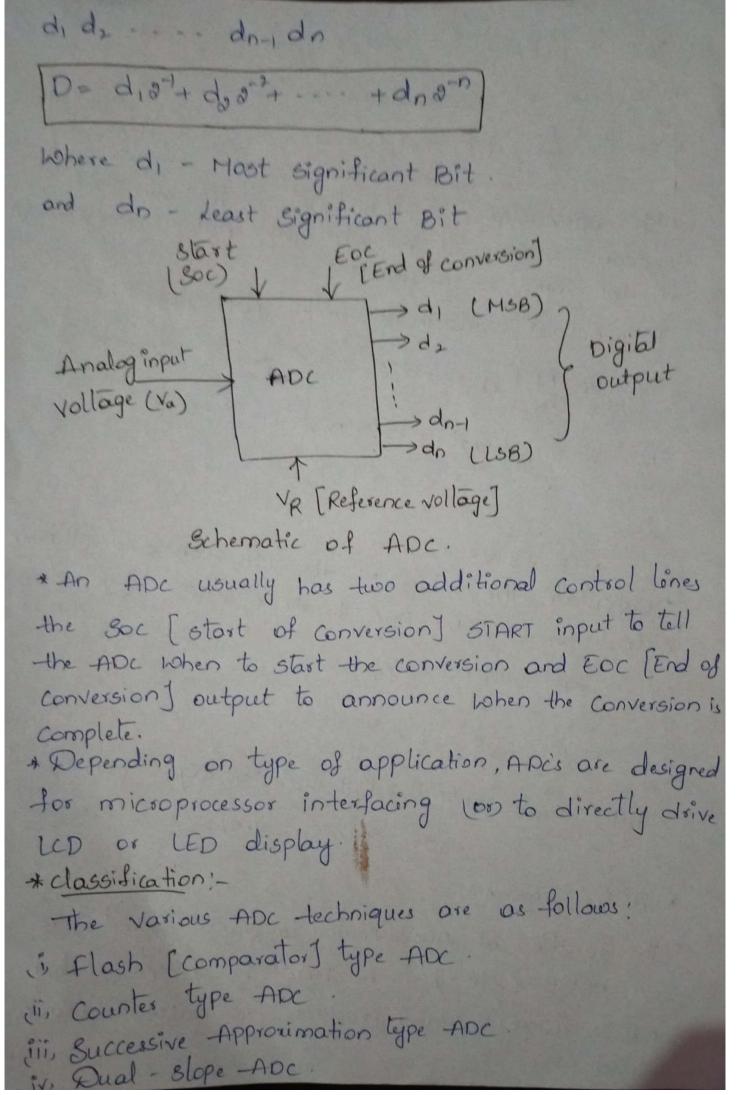

\*A time interval is proportional to phase difference One can measure phase angles from 0° to 360 with such circuit.